高速信号の伝搬と特性インピーダンス:高速シリアル伝送技術講座(13)(3/3 ページ)

有限空間での特性インピーダンス

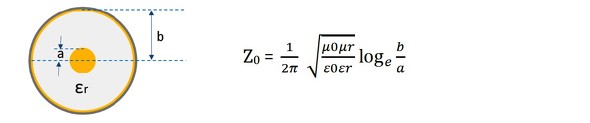

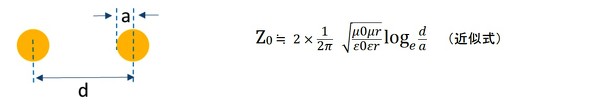

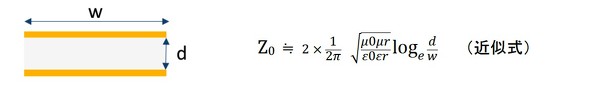

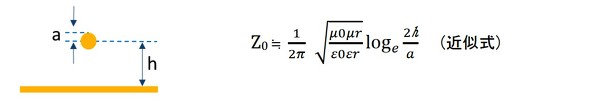

図6aから図6eの同軸ケーブルa、並行線b、並行板c、下部にGNDのある単線d、PCBのストリップラインeなど、電場と磁場が有限の空間内で発生する環境では、電場磁場で結合する部分の長さと距離の2つの比率を自然対数の係数として追加し、特性インピーダンスを表すことができます。

- 図6a:同軸ケーブルでは信号銅線の半径aとシールドまでの距離b(または銅線直径2aとGND直径2b)

- 図6b:並行線では銅線の半径aと距離d(または直径2aと距離2d)

- 図6c:並行板では並行板の幅wと距離d

- 図6d:下部にGNDのある単線では単線半径aとGNDとの距離hの2倍(または直径2aと4h)

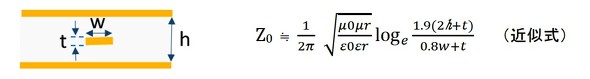

- 図6e:PCBストリップラインではt(厚さ)=0の時、配線幅wの8割とGNDまでの距離hの3.8倍(1.9×2h)

それぞれの構造の特性インピーダンスはZ0の式で分かるように√(μ0μr/ε0εr)で示される基本的な電場、磁場の比率と、自然対数(loge)部の電場・磁場の結合の長さとその距離の比率で構成されています。このように閉空間の特定の誘電体で満たされた環境の特性インピーダンスも結局は電場と磁場の比率を元に出来上がっていることが分かります。

ちなみに図6a〜図6eの各構造の特性インピーダンスの一般的な近似式では、比透磁率をμr=1とし√(μ0/ε0)の部分を計算して120πや376.8Ωを代入し表示される場合が多いようです。

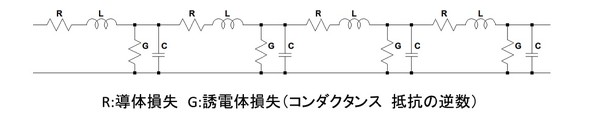

今回は高速伝送で重要な特性インピーダンスの基本的な概念ついて説明しました。特性インピーダンスは電場と磁場の比率が元になっていることが、理解できたのではないでしょうか? 伝送路の限定空間での電場・磁場による信号伝達の振る舞いは誘導性リアクタンス jXl=jωLと容量性リアクタンスjXc=1/jωCに変換できるため、インダクターとキャパシターを用いても表現可能になります。そのため電気工学では伝送路を図7のような分布乗数回路で表現しますが、高速信号は銅線表面を介して電場・磁場(もしくは電磁ポテンシャル)により発生しているため、LCRG回路の電気的な時定数での伝送路の表現方法は代替え的な表現である事も分かったのではないでしょうか。

【参考文献】

・National Semiconductor LVDS Owner’s Manual Rev 3 and 4

・DesignCon 2016, 25G Long Reach Cable Link System Equalization Optimization Xilinx Inc.

・よくわかる電磁気学 (東京図書) 前野昌弘

筆者Profile

河西基文(かわにし もとふみ)/ザインエレクトロニクス シニアエキスパート

ナショナルセミコンダクタージャパンやジェナムジャパンなど、25年にわたり高速通信系半導体の製品開発・サポートおよびマーケットの開拓に従事。伝送路を含んだ半導体の高速設計手法が確立されていない時代に、LVDSオーナーズマニュアルの作成など、同マーケットの成長・普及に寄与してきた。

現在は日本のSerDes製品開発の先駆者的存在のザインエレクトロニクスで、プロダクトマーケティング・開発支援や人材育成などを行っている。

関連記事

デジタル方式のイコライザー「FFE」「DFE」の概要

デジタル方式のイコライザー「FFE」「DFE」の概要

民生機器の高速インタフェース(I/F)としても使われ始めたデジタル方式の信号補償技術であるFFE(Feed forward Equalizer)とDFE(Decision feedback Equalizer)について説明します。FFE/DFEの概要や動作の仕組みを紹介します。 伝送路の特性とシグナルコンディショナーによるジッタの補償

伝送路の特性とシグナルコンディショナーによるジッタの補償

今回は伝送路の減衰特性によるジッタ、伝送路の最適な設計方法、半導体デバイスによるジッタの補償とその仕組みについて説明していきます。 高速シリアル伝送におけるジッタの種類とその特長

高速シリアル伝送におけるジッタの種類とその特長

前回は高速シリアル伝送で使用されるSerDes(シリアライザ・デシリアライザ)について説明しました。今回はSerDesなどの高速シリアルI/Fで、波形測定の際に観測されるジッタの種類とその特長について説明していきます。 PCIe、USB、Ethernet、HDMI、LVDSなど高速伝送技術の基本を理解するために

PCIe、USB、Ethernet、HDMI、LVDSなど高速伝送技術の基本を理解するために

本連載では、さまざまな高速通信規格に使用されている物理層の仕組みや性能、SerDesの機能や特徴とその種類、高速伝送での主要なパラメーター、伝送路を含んだ技術や設計手法などを分かりやすく解説していく。 差動信号伝送のメリット ――使用されている技術と注意点

差動信号伝送のメリット ――使用されている技術と注意点

高速シリアル伝送技術について基礎から学ぶ本連載。2回目は、差動信号伝送の特徴、メリットに焦点を当て、使用されている技術や注意点について解説していきます。 高速伝送の代表的な物理層 LVDS・PECL・CML

高速伝送の代表的な物理層 LVDS・PECL・CML

今回は、高速差動伝送で使用されている代表的な物理層である「LVDS」「PECL」「CML」の特長、接続方法、用途例を紹介していきます。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

図6a:同軸ケーブルの特性インピーダンス

図6a:同軸ケーブルの特性インピーダンス 図6b:平行線の特性インピーダンス (a<<dの場合)

図6b:平行線の特性インピーダンス (a<<dの場合) 図6c:並行版の特性インピーダンス (d<<wの場合)

図6c:並行版の特性インピーダンス (d<<wの場合) 図6d:下部にGNDのある単線の特性インピーダンス (a<<hの場合)

図6d:下部にGNDのある単線の特性インピーダンス (a<<hの場合) 図6e:ストリップラインの特性インピーダンス

図6e:ストリップラインの特性インピーダンス 図7:伝送路 LCRG分布定数回路

図7:伝送路 LCRG分布定数回路