クロックが高精度AーDコンバーターに与える影響:アナログ設計のきほん【ADCとノイズ】(10)(2/3 ページ)

クロック相互変調

クロック相互変調によっても、クロック源がADCのノイズ特性に影響してシステムのノイズが増加します。ほとんどすべてのDAQシステムに、クロック入力が必要なスイッチング部品が多数含まれていますが、場合によっては、別々のクロック源から生成される異なる入力周波数のクロック入力が必要になるかもしれません。

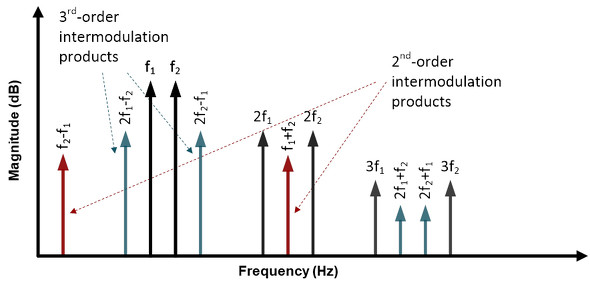

これらのクロック源が個別の部品で非同期の場合は、互いに結合して周波数スペクトラムにトーンが生成される可能性があります。2つのクロック源の周波数をF1、F2として、これらの基本周波数の差または和から相互変調トーンが発生します。図3に示すこれらのトーンは、2次相互変調歪みと呼ばれます。

さらに、基本周波数の和または差と、その高調波を含めた別の相互変調歪みからも、より高次のトーンが発生します。対象の信号帯域幅を超えたところにこれらのトーンが存在したとしても、ADC通過帯域に折り返して、SNRや全高調波歪みなどのAC仕様を悪化させる可能性があります。

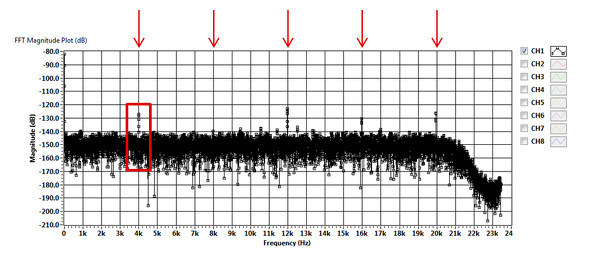

図4の高速フーリエ変換(FFT)には、この相互変調の影響が見られます。入力を短絡したADC(0Vの差動入力)を使用し、プロセッサのクロックは12MHzに設定して、ADCの変調器のクロックを11.996MHzに下げました。これにより4kHzの差が生じます。

プロセッサとADCのクロックの差により、4kHzで周波数スペクトラムに2次相互変調トーンが現れ、4kHzの倍数に高調波も見られます。このことは、相互変調歪みがADCの通過帯域に直接入ってノイズの要因になりうることを示しています。

この影響を軽減するために、広帯域アプリケーションでは、システムで使用する全周波数を1つのクロック源から生成し、それらすべての同期を保証することがよく行われます。他にも、対象の信号帯域幅内でトーンが生成される恐れが最も少ないクロック周波数とサンプリングレートを選ぶ方法もあります。

Copyright © ITmedia, Inc. All Rights Reserved.