クロックが高精度AーDコンバーターに与える影響:アナログ設計のきほん【ADCとノイズ】(10)(1/3 ページ)

クロックが高精度A-Dコンバーターにどう影響するかを深く理解するために、クロック信号に関連する3つのトピックスについて考察します。トピックスとは「クロックジッタ」「クロック相互変調」「クロックに関する基板レイアウトのベストプラクティス」の3つです。

前回(連載第9回)で述べたように、データ収集(DAQ)システムにはすべて基準点が必要です。第9回でのその基準点は、出力コードの生成のためにアナログ入力信号と比較される電圧レベルでした。しかし、DAQシステムには別の種類の基準点も必要であり、それは必ずしも電圧に関連したものではありません。

DAQシステム内では、すべてのコンポーネントが同期して動作できるようにする時間的基準としてクロックが使用されます。A-Dコンバーター(ADC)に関して言えば、クロックが正確で安定していることによって、ホストがADCにコマンドを送り、ADCがホストからコマンドを受け取る際に、それらが正しい順序で、データの破損なしで行われることが保証されます。さらに重要なのは、システムのクロック信号により、ユーザーがいつでも必要なときに入力をサンプリングし、データを送信できることで、システム全体が意図した通りに動作することです。

クロックのことをデジタル入力信号だと考えているかもしれませんが、クロックは高精度DAQシステムのアナログ性能に影響する可能性があります。クロックが高精度ADCにどう影響するかを深く理解するために、クロック信号に関連する以下のトピックを取り上げます。

- クロックジッタ

- クロック相互変調

- クロックに関するプリント基板(PCB)レイアウトのベストプラクティス

クロックジッタ

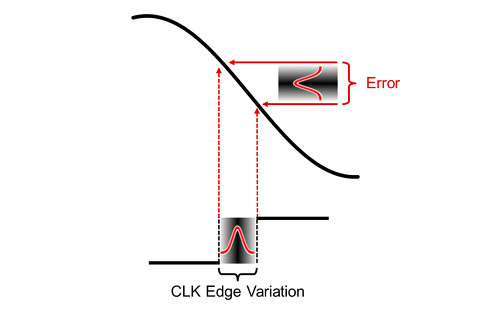

ADCのサンプリング周期が完全に一定であることを期待しているかもしれませんが、理想とのずれが幾分かはあります。「クロックジッタ」とは、ある周期から次の周期までのクロック波形のエッジの変動量を意味します。すべてのADCがクロックエッジを使ってサンプリング点をコントロールするので、クロックエッジの変動によりサンプリングされるものにずれが生じます。このずれの結果、サンプリング周波数が一定でなくなり、新たなノイズ源として変換結果に表れます。

本連載でこれまで取り上げたほとんどのノイズ源と同様に、クロックジッタもランダムに発生し、ガウス分布に従います。そのため、サンプリングの不確定性誤差もガウス分布であり、熱ノイズと同じ振る舞いになります。最終的に、ADC性能に与えるクロックジッタの影響により、主にADCのノイズフロアが上昇し、シグナルチェーンの総熱ノイズの増加につながります。図1は、正弦波入力信号上にクロックジッタにより生じたサンプリングエッジの変動を表したものです。

熱ノイズがどの程度増加するかは、入力信号のスルーレートとクロック源のクロックジッタの量により変わります。ADCの信号対雑音比(SNR)の理論的な上限は、式1を用いて計算できます。

SNRUpper Limit=−20×log10(2×π×fIN×tJITTER) …式1

ここで、fINは入力信号周波数、tJITTERはクロック源のジッタの仕様です。信号の周波数成分が高くなると、入力信号のスルーレートが上昇し、クロックジッタによりSNRが悪化することが予想できます。

デルタ-シグマADCのようなオーバーサンプリングコンバーターの重要な利点の1つに、オーバーサンプリング比(OSR)が高いと、理想的なSNRが改善することがあります。オーバーサンプリングにより、ある決まった期間の複数の変換から平均を取るので、クロックジッタで生じるサンプリング変動もいくらか平均化されます。式2を使って、オーバーサンプリングにより改善するSNRの量を定量化します。式2は単に、デルタ-シグマADCのOSRに依存する項を式1に追加したものです。

SNRUpper Limit(Oversampling)=−20×log10×(2×π×fIN× tJITTER)+10×log10×(OSR) …式2

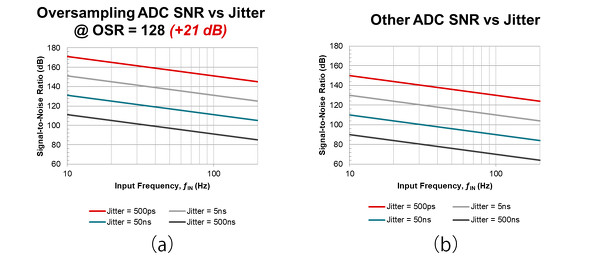

オーバーサンプリングADCとオーバーサンプリングでないADCの性能の違いを図で示すために、図2に入力信号周波数とジッタの関数として式1と式2をプロットしました。それぞれのプロットには、クロックジッタ仕様の異なる4つのグラフが含まれます(0.5ナノ秒[=500ピコ秒]、5ナノ秒、50ナノ秒、500ナノ秒)。図2aがオーバーサンプリングADCのSNR、図2bはオーバーサンプリングアーキテクチャを持たないADCです。

オーバーサンプリングの恩恵があるので、図2aの4つのプロットでは、それに相当する図2bのジッタ仕様のグラフと比べて、21dBの改善が見られます。しかし、プロットは両方とも、入力信号周波数を上げるかクロックジッタの量が増えるとSNRが低下するという、同じ現象を表しています。したがって、SNR目標が高いアプリケーションでは、ジッタを最小限に抑えるための高価でパワーのあるクロックソリューションが必要になることがあります。

例えば、512kサンプル/秒、24ビット分解能のデルタ-シグマADC「ADS127L01」用評価モジュール(EVM/Texas Instruments製)では、の低ジッタ発振器「ASEMB-16.000MHZ-XY-T」(Abracon製)を使用しています。この発振器の標準期間ジッタ仕様は5ピコ秒と、図2でプロットしたどのジッタ仕様よりもかなり低いものです。しかし、コストと性能のトレードオフを考慮すると、本当にこの発振器が必要なのか、高性能すぎるのではないかと悩むかもしれません。

この問いに答えるために、表1でADS127L01のデータシートのノイズ仕様を比較します。「ワイドバンド1」デジタルフィルター設定を使用し、5ピコ秒と500ピコ秒のクロックジッタに対するSNR上限を計算しました。SNR上限の計算には、デジタルフィルターの通過帯域周波数を、最大入力信号周波数を表す「fIN」として使用します。この周波数のときに、クロックジッタの影響が最も顕著に現れます。

tJITTER=5ピコ秒のときは、算出したすべてのSNR値がADCのデータシートのSNR仕様を超えています(緑字で示したセル)。このクロック源を使った場合、クロックジッタからのノイズはシステムの主要なノイズ源にならない、と想定しても大丈夫でしょう。これを、ADCのSNR仕様を下回るSNR値を示す、赤字で示したセルと比べてみましょう。これらはすべてtJITTER= 500ピコ秒の場合です。この場合、信号帯域幅をフルに使用するときにADCが達成できるSNRは、実際にクロックジッタのノイズにより制限されることになります。

| 動作モード | データ・レート (SPS) | OSR | 通過帯域(kHz) | ADC SNR (dB) (データシート) |

SNRUpper Limit (dB) (tJITTER=5ps) |

SNRUpper Limit (dB) (tJITTER=500ps) |

|---|---|---|---|---|---|---|

| 高分解能 | 512,000 | 32 | 230.4 | 103.7 | 117.9 | 77.9 |

| 256,000 | 64 | 115.2 | 107.3 | 126.9 | 86.9 | |

| 128,000 | 128 | 57.6 | 110.4 | 135.9 | 95.9 | |

| 64,000 | 256 | 28.8 | 113.4 | 145.0 | 105.0 | |

| 低消費電力 | 256,000 | 32 | 115.2 | 103.9 | 123.9 | 83.9 |

| 128,000 | 64 | 57.6 | 107.6 | 132.9 | 92.9 | |

| 64,000 | 128 | 28.8 | 110.7 | 141.9 | 101.9 | |

| 32,000 | 256 | 14.4 | 113.7 | 151.0 | 111.0 | |

| 超低消費電力 | 128,000 | 32 | 57.6 | 104.1 | 129.9 | 89.9 |

| 64,000 | 64 | 28.8 | 107.8 | 138.9 | 98.9 | |

| 32,000 | 128 | 14.4 | 110.9 | 148.0 | 108.0 | |

| 16,000 | 256 | 7.2 | 113.9 | 157.0 | 117.0 | |

表1と図2から分かるもう1つの重要な点は、OSRの上昇(ADCの出力データレートを落とすのと同じ意味)によりSNR性能がさらに向上することです。一般に、低い出力データレートに対応できるシステムは、動きの遅い入力信号を測定していることになります。これらのシステムでは事実上、クロックエッジのわずかな変動に「気付かない」ので、ジッタによるノイズが少ないように見えます。

最後に、クロックジッタで生じるノイズを低減するもう1つの方法は、例えば「ADS131A04」など、内蔵のクロック分周回路を使用して変調器のサンプリングクロックを生成するADCを選ぶことです。クロック分周回路は、2つの入力クロックエッジのうちの1つ(通常は立ち上がりエッジ)でのみ働き、元の入力クロック周波数の半分以下の出力クロック周波数を生成します。当然ながら、ジッタによっては両方の入力クロックエッジで発生すると考えられるため、クロックを半分に分割すると、事実上出力クロックのジッタを低減することになります。続けて何回も入力クロックを分周すると、ADCに与える入力クロックのジッタの影響はさらに低くなります。

Copyright © ITmedia, Inc. All Rights Reserved.

図1:ジッタによるサンプリングエッジの変動を示すクロック信号

図1:ジッタによるサンプリングエッジの変動を示すクロック信号