セラミックキャパシター(3) ―― 特徴と構造、製造工程:中堅技術者に贈る電子部品“徹底”活用講座(47)(2/2 ページ)

セラミックキャパシターの主な製造工程

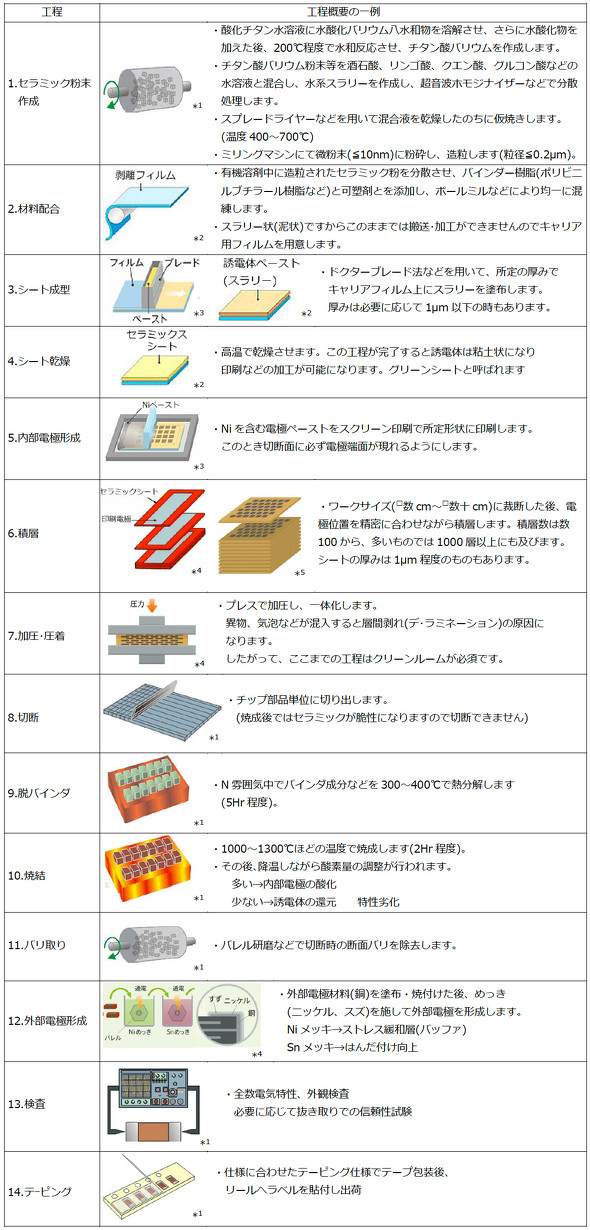

現在の主力である多層セラミックキャパシターは概ね表3に示す工程で作られます。QC工程表や工場見学などの参考にしてください。また設備名についてはフェライトの第3回の稿も参考にしてください。

表3:多層セラミックキャパシター(MLCC)の主な製造工程 (クリックで拡大)

表3:多層セラミックキャパシター(MLCC)の主な製造工程 (クリックで拡大)注)ここで説明した内容は説明用の一例です。実際の内容は使用材料や処理条件などによって変わります。

【出典】

*1:https://en.wikipedia.org/wiki/Ceramic_capacitor

*2:http://www.lintec.co.jp/products/electronics/coated_film.html

*3:https://www.jp.tdk.com/tech-mag/condenser/005

*4:http://www.tdk.co.jp/news_center/publications/capacitors_world/pdf/aaa70516.pdf

*5:http://codezine.jp/article/detail/3740/

特に注目すべき技術は6の積層工程です。電極位置を合わせながら1μm程度のグリーンシートを1000層も位置ずれすることなく積層する製造技術は非常に高度な技術といえます(家庭用のラップフィルムの厚みは10μm程度です)。

一方、リード付き円板形キャパシターの大まかな製造工程は次のような流れになります。

- 材料配合が完了した工程2の後に円板形状に加圧成型します。

- 複数回の焼結工程9、10を経た後に両面にペースト状の銅、銀などの電極材料を塗りムラがないように塗布し、再加熱(600〜800℃)してセラミックと一体化させます。沿面距離の要求などからこの円板型電極の塗布精度が求められる場合には電極の印刷にレジスト法を用いたり、生成電極へのレーザートリミングが行われたりします。

- この円板電極にスズメッキされたリード線をはんだ付けし、さらに本体をエポキシ樹脂などでディップした後に硬化させ完成させます。完成後は電気特性や外観チェックを経てテーピングされて出荷されます。

粒径やシート厚みはここで紹介した材料の技術や製造技術などの日々の改善によって日進月歩で微細化、薄膜化が進んでいます。例えば近年(2020年6月30日)のアナウンスでは0402サイズ(L0.4×□0.2)で下記の仕様のものが発表されるなど、10年前とは桁違いの容量が実現できています。

温度特性*:−55℃〜+85℃/±15%

4VDC:1μF±20%

*発表資料ではX5R(EIA)ですがJIS-C-5101-22:2014やIEC60384-22:2011の2R2特性です。

この製品の耐圧は4Vですが耐圧は何百層とある各セラミック基材の内、最も耐圧の低い基材で決まります。つまり、小型化を実現するには積層する各セラミック基材の厚みをいかに均一に薄くするかが重要になります。表3の工程のはんちゅうで言えば粒径分布、分散度、スラリー塗布厚みなどすべての技術で高精度が求められます。

また、このような微小な部品は多層基板の層内に組み込んで回路の一部を構成したり、高密度実装などに用いられたりしますが微小部品を高密度に実装するには導電性ペーストやクリームはんだの選択、はんだの粒径分布、セルフアライメント性、フラックスの特性、はんだ印刷機の精度、チップマウンターの装着精度にも高度な管理が求められます。これらは対応設備を購入したからといって一朝一夕で実現できるものではなく、実際の管理ポイントを把握するには膨大な経験が必要なのです。

次回はセラミックキャパシターの温度特性の読み方について説明します。

執筆者プロフィール

加藤 博二(かとう ひろじ)

1951年生まれ。1972年に松下電器産業(現パナソニック)に入社し、電子部品の市場品質担当を経た後、電源装置の開発・設計業務を担当。1979年からSPICEを独力で習得し、後日その経験を生かして、SPICE、有限要素法、熱流体解析ツールなどの数値解析ツールを活用した電源装置の設計手法の開発・導入に従事した。現在は、CAEコンサルタントSifoenのプロジェクト代表として、NPO法人「CAE懇話会」の解析塾のSPICEコースを担当するとともに、Webサイト「Sifoen」において、在職中の経験を基に、電子部品の構造とその使用方法、SPICE用モデルのモデリング手法、電源装置の設計手法、熱設計入門、有限要素法のキーポイントなどを、“分かって設計する”シリーズとして公開している。

関連記事

セラミックキャパシター(2) ―― 誘電体とは

セラミックキャパシター(2) ―― 誘電体とは

今回は、そもそもですが、誘電体とは何かについて説明します。 アルミ電解コンデンサー(8)―― 市場不良と四級塩問題

アルミ電解コンデンサー(8)―― 市場不良と四級塩問題

今回は湿式アルミ電解コンデンサーの残った課題として四級塩*問題を取り上げたいと思います。四級塩問題については現象の説明だけの資料が多く、そのメカニズムについては納得できる技術資料がほとんどありません。本稿では筆者が納得しているメカニズムを1つの説として説明をしていきます。 アルミ電解コンデンサー(7)―― 複数負荷モードでの寿命計算

アルミ電解コンデンサー(7)―― 複数負荷モードでの寿命計算

今回は複数の負荷モードが繰り返される場合の機器の寿命をいくつかの負荷モードに区分して考えます。 アルミ電解コンデンサー(6)―― ドライアップ寿命

アルミ電解コンデンサー(6)―― ドライアップ寿命

電解コンデンサーを使いこなす上で避けて通れないドライアップ寿命、いわゆる寿命について説明します。寿命設計は正しく設計しないと数年後に市場でパンクや液漏れなどの不具合を招きます。 アルミ電解コンデンサー(3)―― 化成処理と巻回

アルミ電解コンデンサー(3)―― 化成処理と巻回

アルミ電解コンデンサーの主要部材であるアルミ箔。今回は、エッチングされた箔の表面に施す化成処理について詳しく説明していきます。 アルミ電解コンデンサー(2)―― 箔の様子

アルミ電解コンデンサー(2)―― 箔の様子

今回はアルミ電解コンデンサーのキーパーツの1つである箔(はく)の様子について詳しく説明していきます。

Copyright © ITmedia, Inc. All Rights Reserved.