SiCパワーMOSFETのスイッチング特性、大電流/高電圧領域の測定で解析精度が向上:SiC採用のための電源回路シミュレーション(2)(2/4 ページ)

大電流/高電圧領域を測定する

それでは、SiCパワーMOSFETのデバイスモデルの精度が低い原因は何なのか。ここで原因として疑うべきポイントが1つある。それは、SiCパワーMOSFETのドレイン電流-ドレイン電圧特性(Id-Vd特性)である。

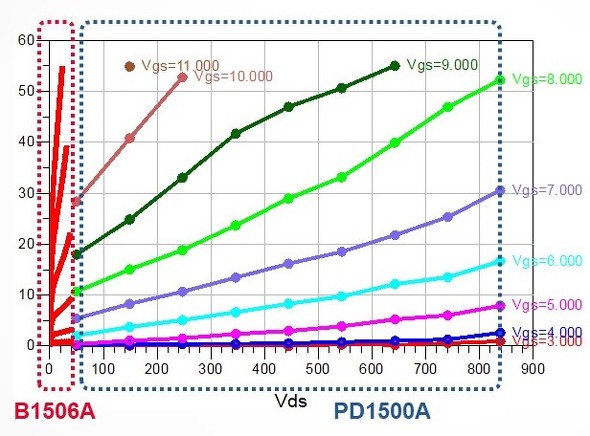

Id-Vd特性は、トランジスタの評価項目として一般的に使われているものだ。ただし、SiCパワーMOSFETなど、大きな電力を扱うパワートランジスタについては、これまで測定できるId-Vd特性の領域が限られていた。なぜなら、パワートランジスタに大きな電力を投入すると壊れてしまう、もしくは発熱によって特性が大きく変化してしまうからである。測定が可能だったのは、ドレイン電圧が最大40〜50V以下と狭い領域に限定されていた(図2)

図2:Id-Vd特性の測定可能領域

図2:Id-Vd特性の測定可能領域従来、キーサイトのパワーデバイスアナライザー「B1506A」を使って測定しても、ドレイン電圧が最大50V以下の狭い領域しかドレイン電流-ドレイン電圧(Id-Vd)特性測定はできなかった。しかし、ダブルパルステスター機能を備える「PD1500A」を使えば、最大1200Vのドレイン電圧と最大200Aのドレイン電流で測定できるため、大電流/高電圧領域のId-Vd特性の測定が可能になった。[クリックで拡大] 出所:キーサイト・テクノロジー

つまり、SiCパワーMOSFETのデバイスモデルは、こうした狭い領域の測定結果を元にフィッティングされていたことになる。言い換えれば、ドレイン電圧が高い領域のId-Vd特性は考慮できていなかったわけだ。ところが前述のスイッチング軌跡は、ドレイン電圧が高い領域も通過する。従って、SiCパワーMOSFETのデバイスモデルの精度が不十分な原因がこのポイントにあると考えるのが妥当だろう。

もちろん、デバイスモデルの作成に関わる技術者は、ドレイン電圧が高い領域のId-Vd特性を考慮すべきだということは以前から分かっていた。しかし従来は、それを測る計測器が存在していなかったため、考慮したくてもできなかった。

図3:ダイナミックパワーデバイスアナライザー

図3:ダイナミックパワーデバイスアナライザーキーサイトが2019年10月に出荷を始めたダイナミックパワーデバイスアナライザー「PD1500A」。ダブルパルステスター機能を備えていることが最大の特徴だ。[クリックで拡大] 出所:キーサイト・テクノロジー

こうした状況は2019年10月に解消された。キーサイト・テクノロジーがダイナミックパワーデバイスアナライザー「PD1500A」の出荷を始めたからである(図3)。この計測器は「ダブルパルステスター」の機能を備えており、パワートランジスタに印加できる電圧は最大1200Vと高く、供給できる電流は最大200Aと大きい。つまり、ドレイン電圧が高い領域のId-Vd特性も問題なく測定できる。

なお、ダブルパルステスターとは、短いパルス幅のテスト信号をパワートランジスタに供給することを目的に開発された計測機能である。実際には、1マイクロ秒(μs)未満のパルス信号を生成して出力するファンクションジェネレーターとオシロスコープを組み合わせることで実現した。パルス幅は最小で100ナノ秒(ns)まで短くできる。この程度のパルス幅であれば、パワートランジスタの発熱を最小限に抑えられるため、高い精度でId-Vd特性を測定できる。このため大電力を供給してスイッチング特性を測定し、その測定結果からドレイン電圧が高い領域のI-V特性を求められる。

Copyright © ITmedia, Inc. All Rights Reserved.