半導体(6) ―― ゲート駆動回路の注意点:中堅技術者に贈る電子部品“徹底”活用講座(65)(1/2 ページ)

今回も引き続き、パワーMOSFETの使い方の失敗事例を紹介します。ただ、当時の日本ではどこも採用していなかったパワーMOSFETの使用方法に関するものですから厳密には失敗事例とはいえないかもしれません。

前回は当方の技術的な見落としとも言うべき失敗事例を紹介しましたが、今回も引き続き使い方の失敗事例を紹介します。

内容的には今日現在半導体メーカー各社から発行されているパワーMOSFETのアプリケーションノート(A.N.)と同等の内容ですが本稿は単なるA.N.の解説ではなく、話の流れとしてはここで紹介する当方の経験を各社がA.N.に反映した結果といえます。記事に該当する当時の日本ではどこも採用していなかったパワーMOSFETの使用方法に関するものですから厳密には失敗事例とはいえないかもしれません。

ゲート駆動回路の注意点

スイッチング電源回路の問題点

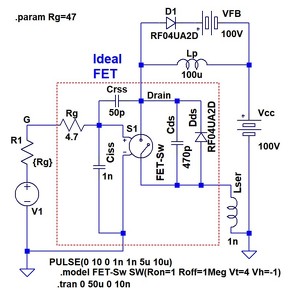

スイッチング電源回路の基本形を図1に示します。

スイッチング回路ではMOSFET(M1)はON/OFF動作のために定常的な損失は少ないのですが状態の切り替わり時に過渡的に発生する電圧/電流の共存領域が新たな損失になります。この損失は切り替わりごとに発生しますので高周波化すればするほど損失が増加します。

この電圧/電流の共存時間を短くしようとする目的でゲート駆動抵抗Rgを小さくしてMOSFETのスイッチングスピードを上げることがよく行われます。ですが高速化は損失の低減と引き換えにEMI(放射)ノイズの増大を伴うので高周波動作を使いこなすにはノイズに関する知識やそれに伴う経験が必要です。

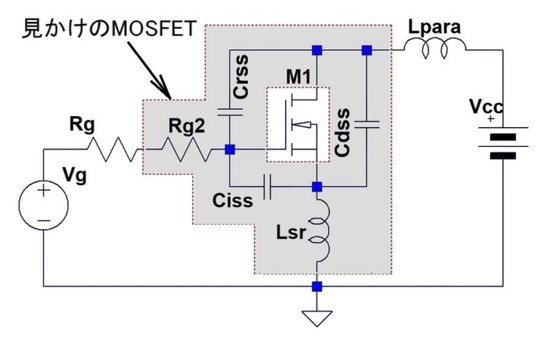

また実際のMOSFETは理想的なスイッチではなく図2に示すように理想スイッチM1の周辺に寄生容量やソースワイヤーのインダクタンスLsrを伴います。加えてトランスにも巻き線の磁気結合の不完全さに起因する寄生インダクタンスLparaも存在します。

つまり、スイッチング電源回路は複雑なLC回路の電流をスイッチM1で強制的に切り替える動作をしていることになります。

高速スイッチングによる異常発振

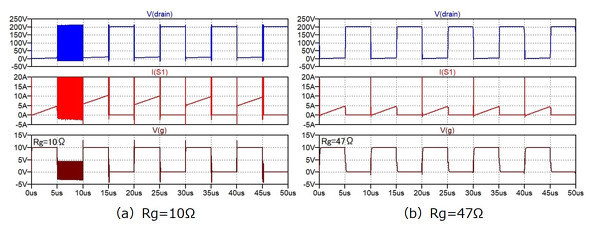

図2に示すようにRgを小さくすると高周波スイッチングが可能になるのですが急激な状態変化はMOSFET周辺の寄生LC共振回路に与えるエネルギー変化も大きくします。MOSFET自身もVth近辺では反転増幅器として作用するので複雑な位相回転の条件によっては図2の回路自身が発振回路として動作することになります。この様子を評価したものが図3の回路です。この回路でゲート駆動抵抗Rgを10Ωと47Ωに切り替えて各部の動作波形を評価しました。

なお、図3の等価回路の不備から現象そのものを完全には再現できていないことをお断りしておきます。

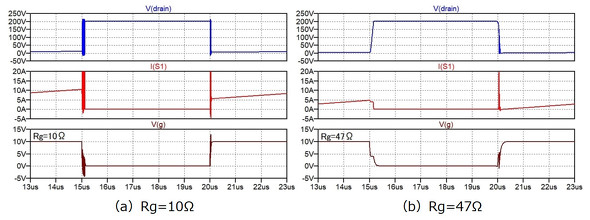

図4からRg=10Ωではドレイン電流の異常振動が認められ47Ωではそのような動作は大幅に軽減されています。図5の詳細なゲート駆動波形を見てみても10Ω時に見られたターンオフ時の異常な振動は47Ωでは見当たりません。

つまりRgが小さい場合は高周波応答が可能なので周辺の寄生素子に残ったエネルギーによる異常な振動にFETが追従して増幅し、異常振動に成長することが分かります。したがって、Rgを大きくすれば高周波応答ができなくなるので振動は増幅されません。

このような動作からFETのスイッチングスピードを調整するためにゲートの駆動信号には一定の遅れ時間が必要であり、目安としてはIdのTf相当の時間(50ns程度)を設ける必要があります。

この現象は浮遊インダクタンスの大きいスイッチング電源、特にフライバック系のスイッチング電源でよく見られますが、配線の浮遊インダクタンスが大きくなるとフォワード系スイッチング電源でも発生の可能性が高くなります。

Copyright © ITmedia, Inc. All Rights Reserved.

図1:スイッチング電源基本回路

図1:スイッチング電源基本回路 図2:MOSFETの実際回路

図2:MOSFETの実際回路