半導体(9)―― MOSFETのアバランシェ耐量の使い方(II):中堅技術者に贈る電子部品“徹底”活用講座(68)(2/2 ページ)

アバランシェ耐量のインダクタンス依存性

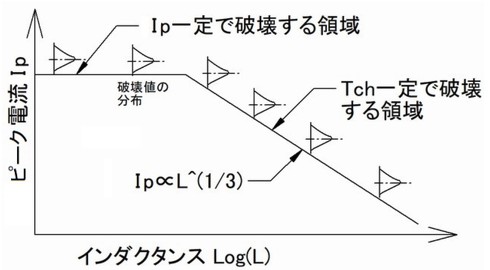

MOSFETのアバランシェ破壊にはここまで説明した寄生トランジスタQ1のターンオンによって起こる破壊現象と、チャネル温度が限界を超えて起こる熱破壊現象が含まれます(図5)。

①(電流一定モード)

図6に示す基本セル中の短絡抵抗Rbeの両端電圧が寄生トランジスタQ1のVbeを超える、つまりブレーク電流が一定値以上になると吸収エネルギーに関係なくQ1がターンオンして破壊します。

②(熱破壊モード)

エネルギーを吸収することでチャネル温度が上昇します。MOSFETのオン抵抗は温度に対して正の特性を持ちますので限界温度を越えると熱暴走を起こして瞬時に熱破壊します。この熱破壊モード時のピーク電流は次のようにインダクタンスに依存します。

(サージエネルギーと温度上昇)

サージエネルギーJ0は3式で計算できます。

このエネルギーはチャネル温度の上昇(ΔTch)を引き起こします。

4式の両辺を2乗して移項すると5式を得ます。

ΔTchが一定とすれば5式の左辺は一定値ですからΔTch一定で破壊するモードの領域では(IP3×L1)が一定、つまりインダクタンスL1が3桁増加するとピーク電流IPが1桁減少することが分かります(図5)。

実際のスイッチング電源においてはMOSFETをこの領域で使用することはありませんがアバランシェ耐量を保証するならこの特性も確認する必要があります。

実際の破壊実力の例を図7に示しますが理論通りに(LP3・IP)一定の領域と電流一定の領域を確認することができます。また電流一定の領域は定格電流Id(dc)の2倍以上あることも同時に確認できます。

一方、図8はアバランシェ機構のメカニズムを理解していない半導体メーカーから提出された保証資料の例ですがいくらメーカーが検査での保証を主張してもこの特性ではチップ自体がアバランシェ機構に対応していませんのでアバランシェ耐量は使用できません。

近年のISO9000の普及に伴い、「検査で取り除けば良い」という安易な思想が公式に認定されたかのようにはびこるようになりましたがこの考え方はとても危険です。メーカーのアバランシェ検査でチップを半殺しにする可能性すらありますので保証の裏付け確認は重要です。半導体メーカーといえどもこのようなことは実際にあるのです。

余談ですが(LP3・IP)一定と実力過渡熱抵抗から算出したチャネル温度は380℃近くになりカタログ値の150℃を大きく超えますがこの値は破壊実力なので保証とは別物です。

またこの領域での破壊は熱破壊モードですからチップ全体にダメージが広がります。ですから不良品を開封すれば故障モードの判別は容易です。

今回はアバランシェ機構の試験(検査)内容についてその背景を説明しました。次回はアバランシェ耐量を使う上でのディレーティングやメーカーでの検査の失敗事例について説明をしたいと思います。

執筆者プロフィール

加藤 博二(かとう ひろじ)

1951年生まれ。1972年に松下電器産業(現パナソニック)に入社し、電子部品の市場品質担当を経た後、電源装置の開発・設計業務を担当。1979年からSPICEを独力で習得し、後日その経験を生かして、SPICE、有限要素法、熱流体解析ツールなどの数値解析ツールを活用した電源装置の設計手法の開発・導入に従事した。現在は、CAEコンサルタントSifoenのプロジェクト代表として、NPO法人「CAE懇話会」の解析塾のSPICEコースを担当するとともに、Webサイト「Sifoen」において、在職中の経験を基に、電子部品の構造とその使用方法、SPICE用モデルのモデリング手法、電源装置の設計手法、熱設計入門、有限要素法のキーポイントなどを、“分かって設計する”シリーズとして公開している。

関連記事

半導体(7) ―― MOSFETのゲート駆動回路の注意点(2)

半導体(7) ―― MOSFETのゲート駆動回路の注意点(2)

今回はパワーMOSFETの構造とそれに起因する寄生容量について説明するとともに、引き続きゲート駆動回路を中心にした使い方の注意事項を説明します。前回の記事と併せて読んでいただければ理解も深まると思います。 半導体(1) ―― 半導体の製造工程

半導体(1) ―― 半導体の製造工程

今回からは電子回路に欠かせない半導体について説明します。本シリーズでは半導体の市場不良および、その原因を説明するための製造工程の問題を主眼に説明をしていきます。 共振子(1) ―― 水晶デバイスとは

共振子(1) ―― 水晶デバイスとは

今回からはマイコンや各種発振器、フィルターに使われる共振子について説明していきます。これらの共振子は回路的には完成度が高く、指定された使い方を間違えなければ正しく動作します。発振器として市販されている部品もありますので適材適所で使い分けることが肝心になります。 電気二重層キャパシター(1) ―― 概要と原理

電気二重層キャパシター(1) ―― 概要と原理

今回からはキャパシターの一種である電気二重層キャパシター(EDLC)について説明していきます。EDLCは、耐圧は低い(数ボルト以下)のですがその容量はファラド(F)単位になり、大容量と言われるアルミ電解コンデンサーの数百倍から数千倍のエネルギー密度になります。 サーミスタ(1) ―― NTCサーミスタとPTCサーミスタ

サーミスタ(1) ―― NTCサーミスタとPTCサーミスタ

今回から「サーミスタ」を取り上げます。サーミスタの分類について簡単に説明するとともに、サーミスタを使用した回路動作の概要について解説していきます。第1回は、NTCサーミスタとPTCサーミスタの違いとともに、NTCサーミスタによる突入電流制限回路について考察します。 フェライト(1) ―― 磁性

フェライト(1) ―― 磁性

“電子部品をより正しく使いこなす”をテーマに、これからさまざまな電子部品を取り上げ、電子部品の“より詳しいところ”を紹介していきます。まずは「フェライト」について解説していきます。

Copyright © ITmedia, Inc. All Rights Reserved.

図5:アバランシェ破壊モード模式図

図5:アバランシェ破壊モード模式図 図6:MOSFETの基本セル構造

図6:MOSFETの基本セル構造

図7:アバランシェ耐量の適合例(600V/8A品)

図7:アバランシェ耐量の適合例(600V/8A品) 図8:アバランシェ耐量の不適合例

図8:アバランシェ耐量の不適合例