発振子よりも、マイコンが高い周波数で動作できるのはなぜ?:Q&Aで学ぶマイコン講座(73)(2/5 ページ)

» 2022年10月13日 10時00分 公開

[小谷豊(STマイクロエレクトロニクス),EDN Japan]

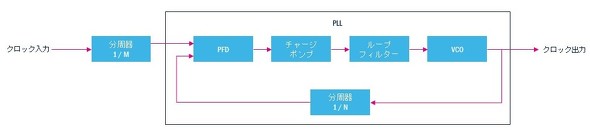

PLLの代表的な回路構成

PLLの構成方法はさまざまですが、代表的な方法として「チャージポンプ式PLL」があります(図1)

チャージポンプ式PLLは、PFD(位相-周波数検出器)、チャージポンプ、ループフィルター、VCO(電圧制御発振器)、分周器で構成されています。

PFDには、位相と周波数両方の違いを検出できるようにするため、フリップフロップが含まれています。チャージポンプは電流掃き出し用の上側のトランジスタと、電流吸い込み用の下側のトランジスタで構成されます。ループフィルターはローパスフィルターで構成されます。VCOはさまざまな構成方法がありますが、代表的な方法としては、電圧-電流変換回路と電流制御型リングオシレーターを組み合わせる方法があります。

分周器には、同期カウンタ方式と非同期カウンタ方式があります。同期カウンタ方式は、フリップフロップのジッタ誤差の累積がない分、非同期カウンタ方式に比べてジッタ誤差が少ないです。一方で非同期カウンタ方式は、後段のフリップフロップが前段のフリップフロップよりも低い周波数で動作するため、同期カウンタ方式に比べて消費電力を削減できます。

チャージポンプ式PLLの動作原理回路

PLLの動作原理について、回路シミュレーターで確認してみます。例として、入力クロックの8倍の周波数のクロック信号を生成するPLLの動作原理回路を示します。

動作原理確認用の回路は、PFD、チャージポンプ、ループフィルター、VCO、分周器(Divider)で構成されています(図2)

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentPR

Pickup ContentsPR

Special SitePR

あなたにおすすめの記事PR