発振子よりも、マイコンが高い周波数で動作できるのはなぜ?:Q&Aで学ぶマイコン講座(73)(3/5 ページ)

» 2022年10月13日 10時00分 公開

[小谷豊(STマイクロエレクトロニクス),EDN Japan]

チャージポンプ式PLLの動作原理

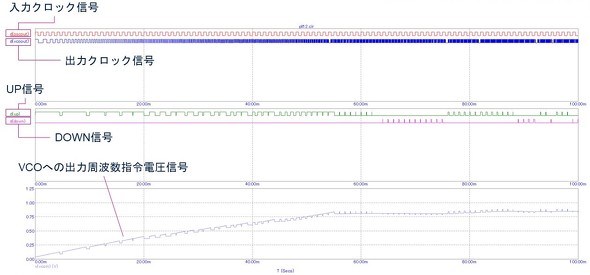

PLLでは、入力クロック信号とVCOの出力信号を、PLL内の分周器で8分の1の周波数にした信号との位相と周波数が一致するようにVCOの出力周波数を制御するため、VCOの出力から入力クロックの8倍の周波数の信号が出力されます(図3)

PFDの動作

PFDは、入力クロック信号とVCOの出力信号をPLL内の分周器で8分の1の周波数にした信号を入力として受け取ります。また、VCOの出力周波数を上げるUP信号および、下げるDOWN信号を出力します。

チャージポンプの動作

チャージポンプは、PFDからUP信号/DOWN信号を入力として受け取り、ループフィルターへ電流を掃き出し/吸い込みます。

ループフィルターの動作

ループフィルターは、チャージポンプから掃き出し/吸い込みされた電流を入力として受け取り、VCO制御電圧を出力します。

VCOの動作

VCOは、ループフィルターから出力周波数指令電圧を入力として受け取り、出力周波数指令電圧に比例した周波数のクロック信号を出力します。VCOへの出力周波数指令電圧は、UP信号がHiの時は上昇、DOWN信号がHiの時は下降、UP信号とDOWN信号がともにLowの時は現状の電圧を保持します。

分周器の動作

分周器は、VCOから出力されたクロック信号を入力として受け取り、8分の1の周波数のクロック信号を出力します。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentPR

Pickup ContentsPR

Special SitePR

あなたにおすすめの記事PR