反転形DC/DCコンバーターの設計(2)部品の定格:たった2つの式で始めるDC/DCコンバーターの設計(16)(3/5 ページ)

半導体の温度計算

温度計算をする意味は既にステップダウンコンバーターの章などで説明しましたが温度(=熱エネルギー)は半導体のみならず、各デバイスのはんだ付けの故障率や信頼性に影響します。いわゆる設計上の重点管理項目です。

図3(a)のように取り付けられた半導体チップに発生した損失はヒートシンクから熱となって空気中に拡散します。この様子を等価な電気回路として表したものが図3(b)の回路であり、式で表すと9式になります。図3や9式の損失P(W)とヒートシンク熱抵抗Rth(H)(℃/W)は設計者が設定できる項目です。

ここで各記号の意味は次の通りです。

P :損失(W)

Rth(J-C):ジャンクション〜ケース間熱抵抗(℃/W)

Rth(H) :ヒートシンク熱抵抗(℃/W)

このFETの損失P(FET)をRONによるPONとスイッチング動作によるP(SW)に分解し、最初にRONによる損失PONを考えます。

RON

FETのオン抵抗です。FETはオン時に抵抗性の物性を示します。FET(M1)がオンしている時、FETにはオン抵抗RONによるジュール損が発生します。ここで使用する電流波形や記号は後出の図6によるものとします。

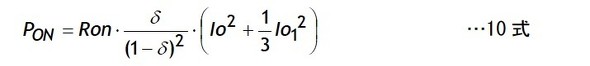

ton中にFET(M1)に流れる台形波の電流I(ON)を矩形波と三角波(励磁電流ΔI)に分解してその実効値(二乗和)をVo、Ioを使って表し、さらに前述のIo1を適用して式を簡素化するとFETのRONによる損失PONは10式になります。

PONを表す10式をδで微分して増減の様子を調べると4式のILPのケースと同じく電流連続モード(Io>Io1)の範囲ではδの増加とともにPONは単調に増加していくことが分かります。ただしFETのRONは正の温度特性ですから高温時の熱暴走を防ぐためにオン損失の計算や温度の実測は最高周囲温度で行います。

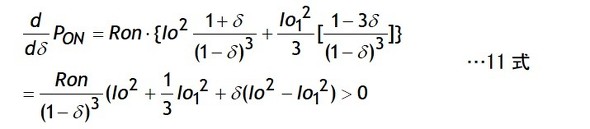

※参考までに10式の微分結果を11式に示します。

11式は電流連続モード(Io>Io1)の範囲ではδによらず正なので10式のPONがδとともに増加することを示しています(0<δ<1)。

このような数式による確認の他に「低入力時に入力電流が増加するので計算するまでもなく11式が成立する」の考え方もあるかと思いますが入力電圧によって台形波の矩形波成分と三角波成分の比率が変化します。この各成分の個別変化を実際に計算してみると10式のカッコ内第2項(三角波成分)はδ=1/3の時に最大損失を示しますが矩形波成分の変化の割合が大きいために総合のPONはδに従って単調増加します。このような背景を踏まえると損失PONやIdPはδとともに増加すると判断できます。

もう一つの損失成分のスイッチング動作による損失P(SW)は1回の動作サイクルごとに発生する損失です。

クロスオーバー(重なり)損失と呼ばれる損失(P(Cr))とドレイン周辺の浮遊容量Cossに起因する損失(P(Co))が含まれます。

P(Cr)損は電圧と電流が共存する時に発生しますのでこの損失の発生タイミングはFETがターンオンして電流を流し始める時とton経過後の電流遮断時です。

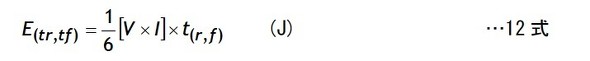

FETの電圧・電流の切り替えが近似的に直線的に行われると仮定するとこのターンオン、あるいはターンオフ1回当たりの損失エネルギーE(tr,tf)は、

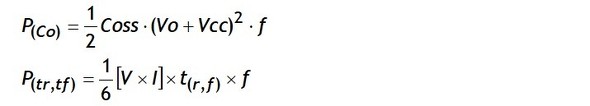

で表せます。ここで[V×I]は(スイッチング前後の電圧×電流)です。t(r)、t(f)は各スイッチング時間です。この12式はスイッチング1回当たりの損失エネルギーですのでスイッチング損失P(tr,tf)はそれぞれ周波数倍したものになります。

加えてチップのドレイン周辺には寄生容量Cossが浮遊します。このCossへの充電エネルギーP(Co)もスイッチングのたびに発生しますのでスイッチング損失PSWに加えます。

したがってオン損失PONまで含めたFETの損失P(FET)は13式になります。

P(SW)を低減するために12式に示すようにt(r,f)を早くすれば損失は低減しますがその反面、発生する電磁ノイズが大きくなります。

このノイズの問題は数ワット程度のソリッド化された小型DC/DCコンバーターでは発生するノイズのエネルギーの絶対量が少ないので多くのケースで問題にはなりませんが、一方、10Wを超えるようなDC/DCコンバーターになると発生するノイズエネルギー量も増加し、安全規格などで問題になるケースが出てきます。その場合には電磁シールドやCRスナバー、EMIフィルターなどの各種ノイズ対策を施すとともにこのt(r,f)を遅めに設定してノイズの発生と効率のトレードオフを考えます。

注)13式から分かるように大形チップではPONは減少しますがチップのCossが増加するのでP(Co)やFETのドライブ電力が増加します。P(Co)はFETのオン/オフごとに発生するので損失P(SW)は周波数依存性を持つことになり、Vccを高くするとP(SW)は大きくなりますがPONは小さくなります。

つまり同じ出力仕様でも入力電圧範囲や動作周波数ごとに最適チップサイズは異なってくるので最適チップサイズを求めるにはこれらの背景を踏まえて実際に測定し比較する必要があります。

Copyright © ITmedia, Inc. All Rights Reserved.