シリコンMOS量子ドットの大規模化 どう実現するのか(前編):imecが解説(2/2 ページ)

300mmウエハーで実現

imecのSiスピン量子ビットデバイスの大規模化への取り組みは、約7年前にSi量子ドット構造向けにカスタマイズされた300mmプラットフォームの開発から始まった。

Si/SiO2ベースのMOSゲートスタックとポリシリコンゲートの最適化およびエンジニアリングにより、1Hzで0.6μeV/√Hzという電荷ノイズレベルを実現した。この値は繰り返しかつ再現性よく実証されている。

最近では、量子コンピューティング企業Diraqとの提携により、imecの300mmプラットフォームをさらに検証した。Nature誌にも掲載されたこの共同研究では、imecのSi量子ドットスピン量子ビットデバイスにおける全ての基本量子ビット操作を、高精度に制御できることが示された。量子ビットの測定操作において、99.9%を超える量子忠実度(Fidelity)が再現性よく達成された。

電荷ノイズも非常に低いことが測定され、これはnpj Quantum Information誌に掲載された以前の論文の結果と一致している。ゲートセットトモグラフィー(GST)測定により残差誤差が明らかになり、低い電荷ノイズ値、量子ビット間の結合、そしてわずかに残存する核スピンを運ぶSi同位体(29Si)が、これらのデバイスの忠実度を制限する主な要因であることが判明した。こうした知見は、Si層に28Siをさらに同位体濃縮することで、より高い忠実度を達成できることを示している。

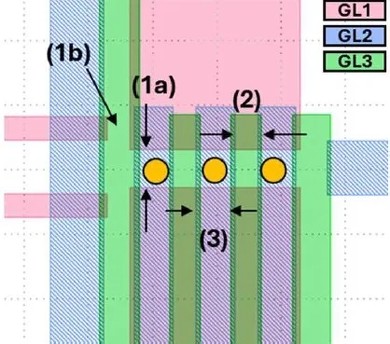

上記の研究では、300mmプロセスが、重なり合うゲートデバイスアーキテクチャを持つスピン量子ビットデバイス向けに最適化された。この手法では、3層のゲートが重なり合い、ほぼ自己整合的な構成でパターン化され、電子を分離し閉じ込める。量子コミュニティーで広く研究、最適化されているこの多層ゲートアーキテクチャは、個々の量子ビットメトリクスや小規模アレイの研究に有用な手段となる。

図3:重なり合うゲートを用いた三重量子ドット設計の図解。電子は黄色の点で示されている。IEDM 2025で発表されたように、ゲートはGL1、GL2、GL3の3つの異なる層に配置されている 出所:imec

図3:重なり合うゲートを用いた三重量子ドット設計の図解。電子は黄色の点で示されている。IEDM 2025で発表されたように、ゲートはGL1、GL2、GL3の3つの異なる層に配置されている 出所:imecアップスケーリングの次なるステップとは

これまでimecは、オーバーラップゲートアーキテクチャの中核となる3層のゲート層を作るために、300mmウエハースケールの電子ビーム描画装置を使用してきました。この300mm対応技術は、設計の柔軟性を高め、量子ドット間のピッチを狭くできるが、描画時間が長いので、300mmウエハー全体を妥当なプロセス時間で描画できないという欠点がある。

IEDM 2025において、imecは初めて、単一プリント0.33 NA EUVリソグラフィを用いて、オーバーラップゲートアーキテクチャの3つのゲート層をパターン形成するデモンストレーションを行った。EUVリソグラフィは現在、最先端の半導体製造プロセスノードにおいて主流になっている。imecの研究は、EUVリソグラフィが優れた量子ドット量子ビットの定義と製造にも同様に使用できることを実証した。これは、Siスピン量子ビット技術の大規模化における大きな飛躍を意味する。

300mmウエハー全体を高い歩留まりとプロセス制御で描画できるようになり、これまでの研究で示された高品質な量子ビットの再現性を最大限に引き出せる。EUVリソグラフィにはさらなる利点がある。電子ビームツールよりも高いオーバーレイ精度でさまざまなゲートを作れるのだ。これは量子ビットの品質向上に役立ち、ドット間のピッチを積極的に制御できるようになる。

⇒(次回に続く)

関連記事

AI分野で欠かせないGPUとは? CPUとの違いや活用例まで解説

AI分野で欠かせないGPUとは? CPUとの違いや活用例まで解説

今回はGPUの構造と歴史、CPUとの違いに関して説明します。 LTspice開発者は、なぜ「QSPICE」も作ったのか

LTspice開発者は、なぜ「QSPICE」も作ったのか

回路シミュレーションソフトLTspiceやQSPICEの開発者として知られるQorvoのアナログエンジニアMike Engelhardt氏が、QorvoにおけるQSPICEの開発やそれがRFやミックスドシグナルにおけるシミュレーションに与えた影響について語った。 チップレット集積「超入門」

チップレット集積「超入門」

今後、着実な成長が見込まれているチップレット市場。本稿では、チップレット集積について「基礎の基礎」をお伝えする。 まだマイコンがなかった、50年前の回路設計の記憶

まだマイコンがなかった、50年前の回路設計の記憶

筆者は約50年前の1974年に大学を卒業して、大手電機メーカーに就職した。初めての仕事は、当時ベンチャー企業だった警備会社に納入される防犯装置の開発だった。入社当時はまだマイコンは広く一般には販売されておらず、主にリレーやトランジスタを使用した回路が設計されていた。この装置開発で面白い不思議な現象を経験した。 トルクが足りないモータードライバーの修理

トルクが足りないモータードライバーの修理

取引先から紹介された会社からモータードライバーの修理を依頼された。不具合の症状は『高速回転は問題なく動作するが、低速回転で逆回転する。低速の正常回転数 0.66に対し現在は0.05』と非常に具体的だった。この症状からするとモーターのトルクが足りてないようだ。依頼者は現場で活躍している人なので、何とか依頼に応えたいと思い修理を引き受けた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

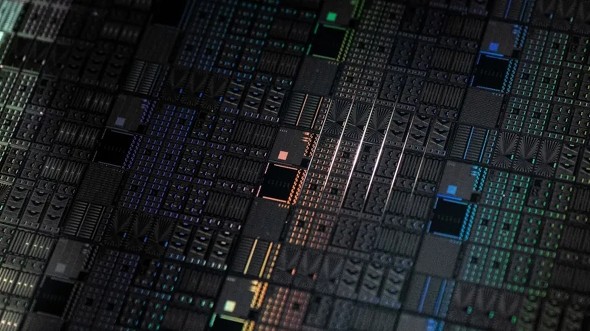

図4:EUVでゲート層をパターン化した後のTEMおよびSEM画像。IEDM 2025で発表された臨界寸法を強調している 出所:imec

図4:EUVでゲート層をパターン化した後のTEMおよびSEM画像。IEDM 2025で発表された臨界寸法を強調している 出所:imec