イーサーネットを産業分野で生かす(3/4 ページ)

遅延の問題

冗長リング構成にも欠点はある。冗長リング構成では、データは目的のノードに達するまでにリング内の各ノードを通過しなければならない。そのため、ネットワーク遅延が増大する。また、今日のイーサーネットスイッチは「保存してから転送する」というアーキテクチャを採用しているので、パケットは転送される前にいったん保存される。そのため、遅延は非確定的な待ち時間を含むものとなる。

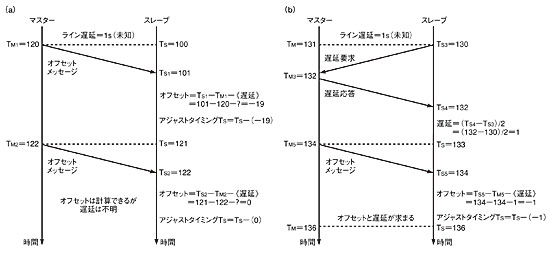

表1に示したのは、1mのカテゴリ5のケーブル上で100Mビット/秒で動作する5ポートのスイッチの遅延を測定した結果である。ここで、総遅延はパケットサイズと内部の転送遅延から、以下の式によって求められる。↓u3eqp300000178h6.jpg

表1に示したように、転送遅延はパケットサイズには依存しない。従って、パケットサイズを固定にすると、スイッチにおける遅延は一定となる。スイッチにおける遅延を減少させるには、パケットサイズを小さく抑えればよい。

EPL(ethernet powerlink)を規定したEPSG(EPL Standardization Group)は、ネットワークにおける遅延ジッターを削減するためには、100Base-TX/FXイーサーネットのリピータハブを使用するとよいとしている。リピータハブはカットスルーのアーキテクチャを採用しており、すべてのパケットを受信する前に、受信済みのパケットを送信ポート以外のすべてのポートに転送する。これにより、遅延を大幅に減少させる。パケットサイズにかかわらず、保存してから転送する方式のスイッチよりも遅延は小さい。

IEEE 1588の利用

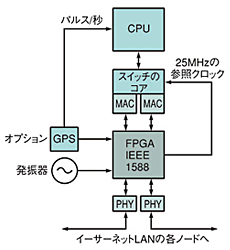

IEEE 1588など、より高レベルのプロトコルを用いれば、上述したのとは別の方法でパケット配信を実現することも可能である。IEEE 1588では、イーサーネットLANにおいてIP(internet protocol)上のUDP(user datagram protocol)パケットを使用することにより、1μs以内の正確な同期を実現する。この性能であれば、動作制御アプリケーションの厳しいリアルタイム要件を満たすことが可能だ。PROFInet、EtherNet/IP、および産業用イーサーネットのグループはみな、ネットワーク同期にこの規格を採用している。図5は、IEEE 1588仕様をハードウエアで実装する典型的な例を表している。

ネットワークの残りの部分の同期を取るには、各ノードがどのクロックソースを使用するかということを決定しなければならない。IEEE 1588では、すべてのノードがBMC(best master clock)アルゴリズムを実行し、タイミングソースを選択することになっている。あるノードがリング内の多数のノードのマスターとなる場合、その設計においては、GPS(global positioning system:全地球測位システム)のような高精度なクロックソースを使用する必要がある。一方、マスターでないノードは、IEEE 1588プロトコルを用いてネットワークからタイミング情報を抽出する。ネットワークからのタイミングソースを利用できない場合、システムにはローカルなタイミングソースを提供するオンボードの発振器が必要となる。また、マスターはネットワークにおけるすべてのスレーブに自分の位置を通知しなければならない。スレーブがそのような通知を受信しなかった場合、そのスレーブは自分自身をマスターとする。

IEEE 1588では、マスターとスレーブの同期にIPマルチキャストに基づくPTP(precision time protocol)を使用する。そのため、PTPパケットを識別するFPGAおよびスイッチコアが必要となる。FPGAは送受信するPTPパケットにタイムスタンプを付加する。受信時には、スイッチは受信したPTPパケットを直接CPUポートに転送する。PTPを使用することで、イーサーネットLANは1μs以内の誤差で同期を取ることが可能になる。

ほかにも、IEEE 1588をソフトウエアとして実装するという手がある。これであれば、FPGAは不要だ。その場合、タイムスタンプの処理はプロセッサが行う。しかし、スイッチの非確定的な遅延を補正するのは難しく、同期の精度が通常10μs〜100μsほどに低下してしまう。そのため、ソフトウエアベースの実装は、動作制御のような高精度のアプリケーションには不向きだ。

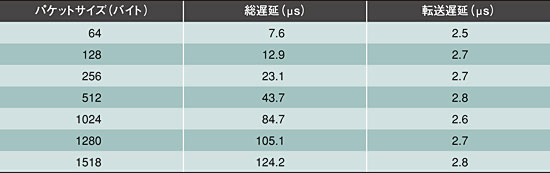

IEEE 1588の同期プロセスでは、まずマスターとスレーブ間のオフセット時間を計算して補正を行う。この機能を実行するために、マスターはスレーブに対して特有のメッセージを、定められた間隔(通常は2秒ごと)で送信し続ける。同期プロセスの第2フェーズは、遅延の測定である。スレーブは、マスターに対して、システムが返す遅延要求を送信し、タイムスタンプを用いて往復遅延を計算する。ここでは、マスターとスレーブ間の遅延が常に対称的であると仮定している。図6(a)、(b)は、PTP同期プロセスのオフセットフェーズと遅延フェーズの例を表している。

Copyright © ITmedia, Inc. All Rights Reserved.

表1 5ポートスイッチの遅延測定結果 1mのカテゴリ5ケーブル上で100Mビット/秒で動作する産業用5ポートスイッチ(Micrel社の「KSZ8995MAI」)を用いた。

表1 5ポートスイッチの遅延測定結果 1mのカテゴリ5ケーブル上で100Mビット/秒で動作する産業用5ポートスイッチ(Micrel社の「KSZ8995MAI」)を用いた。 図5 IEEE1588の実装方法

図5 IEEE1588の実装方法