PCI Expressの可能性を探る:基幹系ネットワーク機器の低コスト化と設計期間短縮に向けて(1/4 ページ)

PCI Expressは拡張性に富み、かつ低コストであることから、基幹系ネットワーク機器の設計において魅力的な選択肢となる。次世代の基幹系ネットワークでは、高コストな独自構造のバスに代わってPCI Expressが選択されるようになるかもしれない。

PCI Express(以下、PCIe)は、すでに汎用コンピュータのペリフェラルバスとしてPCIに取って代わった。そして現在ではスイッチャ、ルーター、交換機などの基幹系ネットワーク機器(以下、ネットワーク機器)での利用が模索されている。PCIeはネットワーク機器に適した基本性能を持ち、コストの面でも今日の主要な独自バスよりはるかに優れている。しかし、従来のようにパソコンに接続していたのでは通信性能が制限されてしまう。PCIeをネットワーク機器で利用するならば、そのアーキテクチャにおける重大な問題点を解決する必要がある。

独自バスの問題点、PCIeの利点

PCIeは、パソコン向けの最新ペリフェラルバスである。前世代のISAバスやPCIバスと同様に、PCIeにはさまざまな機器の設計者が注目している。特にPCIeは従来のバスとは異なり、最新のプロセッサに見合うレベルの性能を満たすだけでなく、それ以上の性能を達成する余地がある。加えて、PCIeはPCIバスとソフトウエア互換性があり、前世代のパソコンの技術をそのまま使用できるというメリットを持つ(別掲記事 「PCI Expressの基礎」を参照のこと)。

組み込みコンピューティング開発者がPCIeを利用した場合、デスクトップコンピューティングの分野で開発された低コストかつ高性能で広く普及した評価済みの技術をそのまま活用できることになる。ネットワーク機器の設計者も高性能で低コストというPCIeの特徴に注目し始めている。従来は、ネットワーク機器の開発において、最大限の性能を達成するために独自のバスアーキテクチャを使用していた。しかし、コストと市場投入時間に対する要求から、独自バスを用いるアプローチは次第に現実的ではなくなってきている。

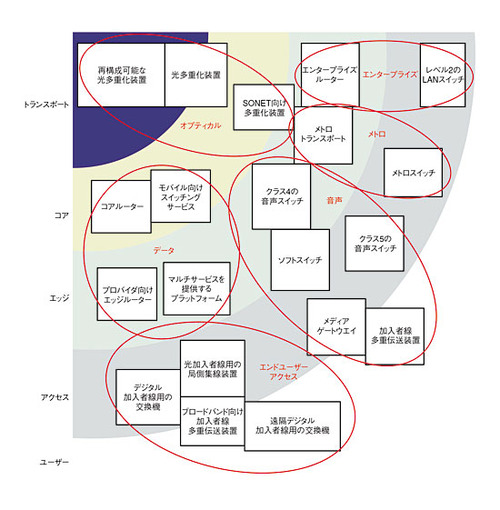

とはいえ、PCIeがネットワーク機器市場に受け入れられるかどうかはまだ確かではない。ネットワーク機器には、トランスポート層やコア層など、ネットワーク階層におけるそれぞれの位置(図1)によって、広範囲にわたる異なる要求が存在する。そのそれぞれの階層には、さまざまな組み合わせのデータ制御/データ処理要件を持つ複数のレベルが存在し、PCIeがすべてに対応できるわけではないからだ。

PCI Expressの基礎

クロック周波数が増加し、クロック線と信号線との間の時間のずれがクロック周期に占める割合が大きくなるに連れ、パラレルバスの実装は困難になってきた。その結果、プロセッサのクロック周波数は1GHzを超えるようになったのに対し、PCIバスのクロック周波数は266MHzで限界に達し始めた。この不均衡とそれによるシステム上のボトルネックを解決するため、PCI-SIGはPCIeを開発した。PCI-SIGの目標は、パラレルバスにおける帯域幅の限界を取り除きつつ、PCIとのソフトウエア互換性を維持することであった。

PCIeバスは、CPUとペリフェラルコントローラなど2つのノード間のポイントツーポイント接続となる並列な数個の「レーン」から構成される。スター型構成の中央にあるマルチポートスイッチにより、従来のパラレルバスで構成可能であったパスの多くがPCIeのポイントツーポイント接続でも実現できる。このスイッチを用いて適切に設計することで、同一のポートを共有しさえしなければ複数のパスを同時に稼働させることも可能である。

PCIeのレーンは、2.5GHzのクロック周波数で8B/10Bエンコードを行うシリアルリンクである。各レーンには転送用および返送用のチャンネルがあり、1レーン当たり合計4本の差動信号を用いる。帯域幅に拡張性を持たせるために、PCIeは1、2、4、8、12、16、32レーンのノード間接続を提供している。これにより、1つのPCIe接続で250Mバイト/秒から8Gバイト/秒までのデータ転送速度が実現可能である。PCIe仕様の次のアップグレード(PCI Express 2.0 Specification)では、シリアルクロック周波数を5GHzまで高めることにより、同じレーン構成で帯域幅容量を2倍にする予定だ。 設計では、レーン数が一致するデバイスを用いる必要はなく、電源投入時の初期化処理や、プラグアンドプレイのボード挿入時にネゴシエーションシーケンスが動作し、ノードが使用するレーン幅を調整する。このため、16レーンのインターフェースを持つデバイスは、16レーンや32レーンのデバイスと全帯域幅を用いて通信することができ、それよりレーン数の少ないデバイスとは帯域幅を減少させて通信することが可能である。

さまざまな幅のシリアルバスと通信しつつ、パラレルPCIバスとのソフトウエア互換性を維持するために、通信モデルの下層レベルにおいていくつかの機能が追加されている。例えば物理層では、データバイトを利用可能なレーン間にストライピングして送信し、受信側で復元するハードウエアがPCIeリンクに含まれる(図A)。シリアルデータパケットには、任意の順序で受信したパケットを正しい順序で復元するためのヘッダー情報が付与され、レーン間の速度差の影響を受けないようにしている。 リンク層は、シリアルリンクにおける送信エラーの検出と、それに対する処置を行う。物理層に送信される各パケットには、エラー検出のためのパケットシーケンス番号とCRC(cyclic redundancy check:巡回冗長検査)コードが含まれ、送信エラーが発生すると、リンク層のハードウエアが破損したパケットを自動的に再送する。

トランザクション層は、PCIバス向けにメモリーマッピングされた場所への読み書きトランザクションを、PCIe向けのコマンドパケットとデータパケットに変換する。各パケットには、特定のトランザクションに関連付けられた固有の識別子が含まれている。この識別子により、データパケットをノードやソフトウエアに送信する経路の選択が可能となる。

トランザクション層は、システム内のメモリー、I/O、構成スペースをサポートし、32ビットアドレッシングと拡張64ビットアドレッシングの両方を扱うことができる。この機能により、PCIeはPCIバスのロードストア型アーキテクチャとフラットメモリー空間を完全に模倣することができ、システム内の上位のソフトウエアレベルでは一切変更の必要がない。つまりPCI用に開発したアプリケーション、OS、ハードウエアドライバを変更することなく、PCIeハードウエアを使用できるのである。

PCIバスには割り込み、電力管理、リセットなどのための制御信号線がある。PCIeではこれらの制御信号線を、メッセージング空間に取り込んで扱う。PCIeインターフェースを持つハードウエアは、このような制御信号線を、コマンドやデータトランザクションと同じようにシリアルリンク上のデータパケットに変換する。PCIeにはこのように制御信号線をパケットとして取り扱うための「仮想線」が用意されている。

加えて、PCIeのアーキテクチャは、既存のソフトウエアを活用できるよう単にPCIバスを模倣するだけではなく、新しい機能も提供する。例を挙げると、パケットに「リラックスオーダリング」や「優先度」などの属性を付加する機能がある。システムはこのような属性を、スイッチの管理や、I/Oリソースに対するノード間競合の解決に用いることができる。つまりPCIeは、VoIP(voice over internet protocol)などの通信アプリケーションで要求されるQoS機能もサポート可能であることになる。

Copyright © ITmedia, Inc. All Rights Reserved.

図1 ネットワークにおける各種機器の位置関係 ネットワークにおけるそれぞれの機器は、それぞれが稼働する階層により、バス要件やPCIeの適用可能性が異なる(提供:IDT社)。

図1 ネットワークにおける各種機器の位置関係 ネットワークにおけるそれぞれの機器は、それぞれが稼働する階層により、バス要件やPCIeの適用可能性が異なる(提供:IDT社)。 図A PCIeのストライピング機能 PCIeの物理層ハードウエアは、後続のデータバイトを空いているレーンに自動的にストライピングし、受信側で正しい順序で復元する

図A PCIeのストライピング機能 PCIeの物理層ハードウエアは、後続のデータバイトを空いているレーンに自動的にストライピングし、受信側で正しい順序で復元する