組み込み向けデバッグ技術の基本(2/3 ページ)

広く普及したJTAG

1985年、欧州企業が集まり、LSIのテストにおける問題を解決するための団体としてJTAG(Joint Test Action Group)を設立した。同団体によりLSIのバウンダリスキャンテストのための規格「IEEE 1149.1(通称JTAG)」が策定され、1990年に発表された*5)。

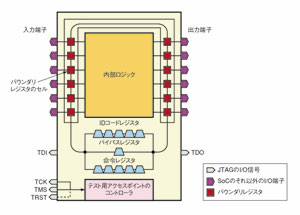

JTAGは、シリアル通信を介して回路のテスト/解析を行うための最大5つの信号I/O(JTAGポート)を定義している。5つの信号とは、TCK(test clock)、TMS(test mode select)、TDI(test data in)、TDO(test data out)、オプションのTRST(test reset)である(図3)。

JTAGに対応したハードウエアは、16状態の有限状態マシンをベースとし、TMS信号がそれを制御する。TMS信号はTCKの立ち上がりエッジで取得する。データ情報はTDIから入力され、TDOから出力される。最終的にはTRSTを用いて全体をリセットする。

JTAGを利用する場合、LSIの各パッドにスキャンレジスタを追加し、それらを内部的に接続してバウンダリスキャンチェーンを構成する。このチェーンに対してTDI/TDOおよびJTAGコマンドによって入出力を行い、基板上の外部接続をテストしたり、LSI内部の論理的接続をテストしたり、パッドの入出力値を取得したり、JTAGチェーンをバイパスモードにしたりすることができる。

JTAGは低コストの機能を提供しており、LSIテスト手法の中でも最もよく使われるものとなった。加えて、使用方法が容易で可用性が高く、低コストで実装できるため、オンチップのデバッグリソースにアクセスするためのデバッグポートとしてもよく利用される*6)。JTAGは、ホスト上で実行するデバッガとプロセッサのデバッグリソースとの間の通信においてトランスポート層として機能する。

ICEのコストが上昇してきたことから、ICEに似た機能を提供するために、多くの半導体ベンダーがより多くのデバッグ用ハードウエアをチップに集積するようになった。このようなオンチップのデバッグ用ハードウエアの代表例には、米Freescale Semiconductor社製の組み込みプロセッサ「68K/ColdFire」に用いられている「BDM(background debugger mode)」がある。ほかのベンダーからも、同様の機能が独自の名称で提供されている。オンチップのデバッグ用ハードウエアにより、従来はICEを介さなければ利用できなかったハードウエアブレークポイント、内部レジスタへのアクセス、メモリーデータの読み書き、ウォッチポイントなどの機能が実現可能になる。

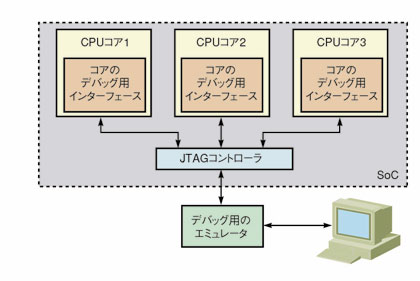

マルチプロセッサ方式のSoCでは、オンチップのデバッグ用ハードウエアの各部品をメインのJTAGコントローラに接続する方法をとる(図4)。接続方法はベンダーによって異なるが、オンチップのデバッグ用JTAG状態マシンとホストデバッガとの間にTDI/TDOによるJTAGチェーンを構成するのが一般的である。

トレース技術の進化

リアルタイムシステムのデバッグにおいては、ハイゼンベルク(Heisenberg)バグ、つまり“プローブ”による影響が大きな問題となる。これは、デバッグやモニタリングのために追加したソフトウエア/ハードウエアが、システムの動作を変更してしまう可能性があるというものである。プロファイリングやデバッグ、モニタリング用の情報を収集するためにソフトウエアを追加すると、この状況が発生する。

デバッグ用ハードウエアを利用する場合にも同様の現象が生じる。例えば、オンチップのデバッグ用ハードウエアは、ブレークポイントを挿入することによりプロセッサの実行フローを変更しているかもしれない。あるいは、プロファイリング用のハードウエアが、プロファイル情報を格納するためにプロセッサの帯域幅の一部を“借用”しているかもしれない。またソフトウエアがUARTによる接続を必要としているときに、デバッグ用ハードウエアがログ情報を記録するためにこのインターフェースを使用しているかもしれない。

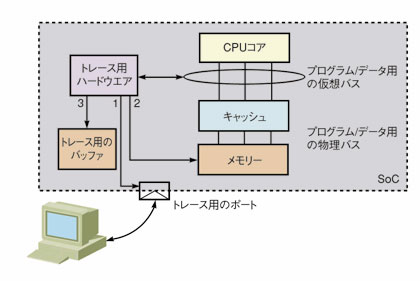

通常、ICEでは本来の動作を妨げないトレース機能が提供されている。同様の機能を提供するために、トレース用のハードウエアをオンチップに集積するSoCベンダーがますます増えてきている(図5)。トレース用ハードウエアでは、トレース専用のハードウエアとポートを用意し、トレースデータ用とプロセッサデータ用のバスを分離して、さらにJTAGインターフェースを設けることで、本来の動作を妨げないようにする。

トレース情報は、トレースポートを用いて取得する。この方法では、トレースボックス(ロジックアナライザ)をトレースポート上に接続し、取得したデータからメッセージを再構成して、それをソースコードに関連付ける。

トレース情報の別の取得手段としては、仮想トレースバッファを使用する方法がある。その場合、プロセッサのメモリーにトレース情報を保存する。例えばテストの終了後に、ホストがJTAGポートを介してそれを取り出すといった形になる。

もう1つの方法は専用トレースバッファを用いるもので、専用メモリーにトレース情報を保存し、テストの終了後にホストがそれを取り出す。

1998年、「Nexus 5001 Forum」という団体が設立された。同団体の設立目的は、組み込みシステム向けのデバッグ手法やツールに関する複数ベンダーの知識と経験に基づき、オンチップのデバッグ機能とインターフェースを標準化することだ。そして、同団体が定めた組み込みプロセッサ向けのデバッグインターフェース規格が「IEEE-ISTO 5001 2003」である。これは、組み込みプロセッサにおけるソフトウエアの開発/デバッグのためのオープンな汎用インターフェースを定義している*7)。具体的には、トレース機能や信号の種類、メッセージング用プロトコル、API(application programming interface)などのトレースインターフェースが標準化された。その一方で、同規格にはベンダーが独自にカスタマイズできるよう、厳格には定められていない部分も存在する。当初は自動車市場をターゲットとしていた規格だが、ワイヤレス市場やネットワーク市場へも急速に普及していった。

脚注

※5…JTAG IEEE Standard 1149.1-2001, Revision of IEEE Standard 1149.1-1990, IEEE Standard Test Access Port and Boundary-Scan Architecture.

※6…Mittag, Larry, "Software Debug Options on ASIC Cores," www.embedded.com.

※7…The Nexus 5001 Forum Standard for a Global Embedded Processor Debug Interface Version 2.0, www.nexus5001.org.

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

図3 JTAGの概念図

図3 JTAGの概念図  図4 マルチプロセッサチップでのJTAGの利用法 マルチプロセッサのチップの場合、デバッグ用ハードウエアはメインのJTAGコントローラと直接通信を行う。

図4 マルチプロセッサチップでのJTAGの利用法 マルチプロセッサのチップの場合、デバッグ用ハードウエアはメインのJTAGコントローラと直接通信を行う。 図5 トレース用ハードウエアの構成法 オンチップのトレース用ハードウエアでは、トレースデータ用とプロセッサデータ用に個別のバスを用意することで、デバッグによって発生する通信を最小限に抑えている。

図5 トレース用ハードウエアの構成法 オンチップのトレース用ハードウエアでは、トレースデータ用とプロセッサデータ用に個別のバスを用意することで、デバッグによって発生する通信を最小限に抑えている。