組み込み向けデバッグ技術の基本(3/3 ページ)

キャッシュへの対応

キャッシュは高い性能を得るための有効な手段である。しかしキャッシュを用いると、CPUの処理の様子が外部メモリーバスでは確認できなくなるため、デバッグ作業は困難となる。また、コアとDMA(direct memory access)/アクセラレーション用ハードウエアとの間の一貫性を理解するのは難しい。

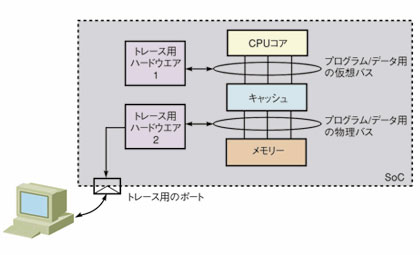

オンチップのトレース用ハードウエアを利用すれば、この問題を解決することができる。また、キャッシュの状況をより詳細に調べるには、キャッシュ処理の前後のバスをトレースするのもよい(図6)。2つのトレース結果を比較すれば、キャッシュが物理バスにアクセスする際にキャッシュミスがあった場合にもそのことを検出できる。これにより、キャッシュミスを減少させ、ソフトウエアの性能を改善することが可能になる。

その他の方法としては、キャッシュのデバッグ用にオンチップのハードウエアを加えて、デバッグモードでキャッシュの内容を読み出したり、キャッシュに書き込んだりするというものがある。通常、この方法ではソフトウエアまたはJTAGポートを介したキャッシュのデバッグ用レジスタを用いる。デバッガを利用すれば、プログラムの実行を一時停止してキャッシュの内容を確認することが可能だ。この情報は、キャッシュの無効化、同期、フラッシュなど、キャッシュデータの消去に関連する問題をデバッグする際に有効である。

複雑なSoCへの対応

最新のSoCでは、1つのチップに複数のプロセッサを集積していることが多い。そのため、従来のデバッグ用ハードウエアでコア同士の相互作用をデバッグするのが困難になってきている。

そうした複雑なマルチコアSoCのデバッグによく使用されるようになってきたのが、最近開発されたデバッグ手法であるクロストリガーである*8)。その原理は、あるコア領域におけるイベントを基に、他のコア領域または同一のコア領域で用いるトリガーを生成するというものだ。よくあるイベントとしては、デバッグモードへの切り替え、割り込みの発生、ウォッチポイント/ブレークポイントへの到達がある。

生成されたトリガーにより、プロセッサ上のトレースを開始/停止することができる。また、いくつかのトリガーを組み合わせることで、エンドユーザーは複雑なデバッグシーケンスを柔軟に作成可能である。クロストリガーを用いれば、例えばコアAがあるプログラムアドレスに達したときにコアBのトレースを開始したり、コアBがデバッグモードに入ったときにコアAの動作を停止させたりすることができる。

SoCのサイズ縮小への要求が高まる中、低コストのデバッグ手法は組み込みシステムの開発者にとって救いとなる。ただし、低コスト化を求めるとしても、決して妥協してはならないことがある。システム内で発生するすべてのバグを予測することはできないので、せめてそれを後から検出できる確率は高めなければならないのだ。オンチップのデバッグ用ハードウエアが低コストになった代わりに、プロジェクトの後工程で、ソフトウエアのデバッグに多くのコストをかける必要に迫られることもあるだろう。

また、デバッグの行いやすさとセキュリティの確保は相反する要求であることも忘れてはならない。メーカーの多くはクラッカー(ハッカー)による攻撃を防ぐために、デバッグ機能を無効にして製品を出荷する。これは実は賢明な処置ではない。将来的に、どのような問題に遭遇するかを予測するのは不可能だからである。キーやヒューズなど、セキュリティを考慮した方法でデバッグ機能へのアクセスを制限するほうが、デバッグ機能を危険にさらさないための賢明な方法だといえる。

脚注

※8…Dannenberg, Andreas, "Hunting for bugs in real-world applications … more than a child's game," www.embedded.com.

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

図6 キャッシュ前後のトレースを可能にする構成 オンチップのトレース用ハードウエアでは、トレースデータ用とプロセッサデータ用に個別のバスを用意することで、デバッグによって発生する通信を最小限に抑えている。

図6 キャッシュ前後のトレースを可能にする構成 オンチップのトレース用ハードウエアでは、トレースデータ用とプロセッサデータ用に個別のバスを用意することで、デバッグによって発生する通信を最小限に抑えている。