どうする?SoCのオーディオ品質:課題は山積み、出口は見えず (5/5 ページ)

より深刻なのは出荷テスト

特性評価がこれほどまでに複雑な問題であるなら、SoCの製造工程における出荷テストが悪夢のような作業になることは想像に難くない。米LSI Logic社のエンジニアリングフェローであるMarcel Tromp氏は、「テストの役割は部品の品質を保証することだ。その一方で、テスト時間は例えば5.5秒以内に抑えなければならない」と問題を指摘する。このテスト時間では、特性評価環境ではお決まりの作業となっているすべての測定を実施することはできない。ましてや、音質の問題をクリアするために、アナログ出力を徹底的にテストする時間などない。しかも、ホームシアター向けのSoCには、10個近くのアナログ出力を備えるものもある。さらに、製造工程のテスト環境の実情や、顧客からのテスト要求が多種多様であるといった問題も存在する。

Wolfson社のFrith氏は、「顧客によっては、チップが優れた音質を実現できる能力を備えていることを無視しているところもある。それなりの出力さえきちんと得られれば、ほかはどうでもよいと思っているのだ」と嘆きつつ、「その一方で、日本のシステムメーカーや自動車業界のように、すべてをテストしようとする顧客もある」(Hayes氏)と語る。つまり、「自分の製品ラインに関連する範囲だけを求める顧客もいれば、すべての特性をAudio Precision社製の装置で測定しようとする顧客もいる」(Hayes氏)ということだ。

製造工程でのテストは、次第に困難になってきている(図2)。Frith氏によると、24ビット、192キロサンプル/秒に対応するアナログ信号をテストするには、米Teradyne社製ミックスドシグナルテスターの最高機種であっても、すべてのダイナミックレンジと、すべてのノイズマージンを食いつぶすことになる。またダイナミックレンジの大きい信号を扱える測定ユニットの数が少ない場合には、アナログ出力を並列にではなく1つ1つ順にテストしなければならない。

Hofer氏は、もう1つの問題点を以下のように説明する。

「高精度のオーディオ機能のテストについては、研究開発部門がテスト環境全体を指定する傾向がある。しかし、今日のように距離や文化の壁を乗り越えての協業が進む世の中では、そのようなことを実現するのは難しい。例えば、中国では、テストシステムが実際にはどこをグラウンドとしているのか分からないような施設も存在した」。

最高の条件でも電気的ノイズが大きいチップにとっては、この状況は最悪である。こうしたことから、テスト設計は“匠の技”となる。特性評価を担当するエンジニアはテストエンジニアと協力し、チップの音質が顧客の要求するレベルである確率を高く保ちつつ、現実的なテスト時間に抑えることができるようにテストの数を最小限に抑えなければならない。オーディオに関する詳細な知識、経験、そして強運がなければ、これを実現することはできないだろう。

「定量的なテスト項目のセットを定義することですら、技術を要するものとなってきた」とLSI Logic社のTromp氏は語る。その上で、「問題なのは、良いか悪いかという非定量的な概念をどうやってエンジニアリングの世界に持ち込むかだ。これは映像に関する問題と同様のもので、最終的な判断はユーザーに委ねられる。しかし、少なくとも映像の場合、何か不具合があればフレームを停止して確認することができる。オーディオでは、それすらも困難だ」(Tromp氏)と続けた。

とはいえ、専門家らは、いくつかの手掛かりを持っているようだ。「テストにおける問題の多くは、経路制御とアクセシビリティの優劣に帰着する」と Hofer氏は指摘する。「アクセシビリティが鍵を握る。例えば、オンチップのD-Aコンバータが存在する場合、その入力側と出力側の両方にアクセスできる必要がある。そうでなければ、内部の動作についてはまったく分からないまま、システムの出力だけを測定することになってしまう」(同氏)ということだ。

ハイエンドオーディオでは、アクセシビリティを実現する設計が重要となる。エンジニアはSoCにおいて、テストポイントを適切に提供しなければならない。また、テスト信号の経路制御には細心の注意を払う必要がある。いずれかに誤りがあると、測定データはほとんど無意味なものになってしまうからだ。さらに、110dBのダイナミックレンジで測定している場合には、クロストークやノイズフロアの高いアナログマルチプレクサなど、重要ではないと思われるいくつかの要因がアナログノードの測定を不正確にしてしまう可能性もある。

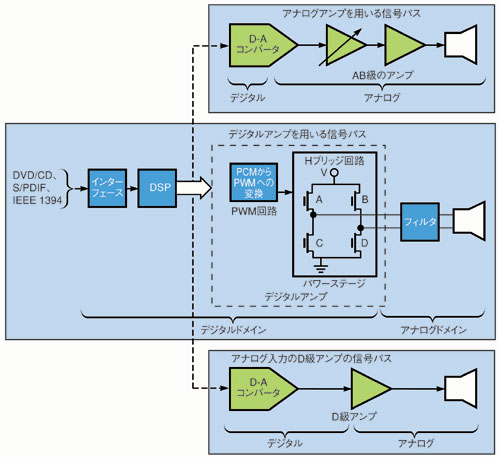

すべての評価項目を完全にテストする時間はない。従って、設計者は故障が生じやすいモードを理解し、その部分が検査しやすいようにチップを設計する必要がある。TI社のShipley氏は、同社のD級アンプ(図3)について、「2次フィルタまではデジタルの世界なので助かった」と語っている。しかし、「そうはいっても、最終的なアナログ信号で生じている問題をデジタル回路のアーキテクチャに関連付けるのは難しい作業だ。テスターを使えばチップのスイッチング波形を観測することはできるが、それと顧客が耳にする音質を結び付けるのはさらに困難だ」(Shipley氏)とその難易度の高さを説明する。

製造工程でのテストを実現するために、SoC設計者は次のようなアプローチをとることになるだろう。まずテストシステムを使用していくつか特定のテストを実施する。その上で、あるベンダーのヘッドホンやD級アンプを使用した場合に、そのSoCチップではどのように聴こえるのかということを調べるのだ。もちろん、これは簡単な作業ではない。しかし、ハイエンドなオーディオの世界では、実際にどのように聴こえるのかというのが最も重要なことである。そのため、 SoCの設計者およびテストエンジニアは、この課題に立ち向かわざるを得ない。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

図2 テスト環境の例

図2 テスト環境の例 図3 D級アンプの内部構成 設計者は、特性評価のためにさまざまな信号経路にテストポイントを用意し、トラブルシューティングが行えるようにしなければならない。

図3 D級アンプの内部構成 設計者は、特性評価のためにさまざまな信号経路にテストポイントを用意し、トラブルシューティングが行えるようにしなければならない。