プリント基板のアクセシビリティを高める:検証/デバッグを容易化するために(3/3 ページ)

CATEGORY 4:デジタル信号

ほとんどの基板において、最も多くの信号線が含まれるのは、外部のホストプロセッサ、基板上のローカルプロセッサ、あるいはFPGAから制御/観測が可能なデジタル信号のカテゴリである。このカテゴリには、ソフトウエアを利用した検証/デバッグ手法を適用することができる。Stretch社のThanawala氏は、「ソフトウエアの役割は重要だ。ソフトウエアを利用して問題を検出することができれば、基板にプローブを当てる必要はない。ソフトウエアを利用した検証を可能にすることを目標とし、われわれのチップ開発チームは、基板の検証担当者に必要となる作業を把握しようと努めている」と述べる。

ARM社のHavens氏も、ソフトウエアを利用しようという考え方に共鳴している。同社は、ARMコアに対応するソフトウエアカーネルやインサーキットエミュレータ、外部デバッグツールを提供している。これらが、単なるデバッグ用ソフトウエアから急速に進化し、普及するのを目にしてきた。すなわち、ARMベースのSoCにおいてすべてを制御/観測する機能と、SoCの外部のチップをも制御/観測する機能が追加されるようになったのである。

そうしたソフトウエアツールが提供されるようになると、検証/デバッグ担当の技術者は直ちにそれを利用し始めた。そして、基板の別の部分からの信号をSoCへと戻すことにより、さらに多くの回路をCPUの制御下に置くようになった。すなわち、ソフトウエアでアクセス可能なレジスタによって、CPUの周辺機能を制御するのである。このようなソフトウエアによるデジタルブロックの制御方式であれば、基板にハードウエアを追加する必要がない。このメリットを享受できるようにするには、検証チームが観測する必要のあるすべての機能をレジスタで実行できるよう、1つ1つ確認していく必要がある。

Stretch社のThanawala氏は、周辺機能またはI/Fの設計に、エラー処理のためのレジスタを取り入れることを提案している。ドライバソフトウエアが問題を検出し、少なくとも診断を開始できるようにするためだ。また、制御の状態とデバイスの内部レジスタをソフトウエアから参照できるようにする必要がある。そのためには、CPUを集積するICの汎用I/Oに、内部レジスタの値を戻す必要があるかもしれない。

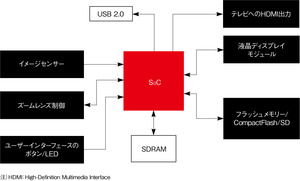

以上のようにすれば、スタンドアロンのマイクロプロセッサであれ、マイクロコントローラであれ、SoC内のCPUコアであれ、プロセッサを基板上のアクセス手段の中心に置くことができる(図2)。

■FPGAの活用

上述したのは非常に有効な考え方だが、実はそれよりもさらに強力な手段がある。それは、FPGAを用いる方法だ。米Xilinx社でプラットフォームマーケティング担当ディレクタを務めるBrent Przybus氏は、「FPGAを使えば、より効果的にアクセシビリティを提供することができる」と述べる。同社は顧客に対し、FPGAをデバッグ用コントローラとして用いるようアドバイスするだけでなく、同社のアプリケーションプラットフォーム戦略にのっとった独自のリファレンスデザインを開発している。

システムの制御に用いるICは、基板上の多くの主要な信号の交差点に位置し、重要な情報を知り得る存在である。FPGAが基板の中心でSoCとして機能する場合も、コプロセッサとして機能する場合も、I/Fとして機能する場合も、システムの中心にあることが多い。

FPGAを用いると、CPUを用いる場合にはない大きなメリットが得られる。そのメリットとは、ハードウエアとソフトウエアの両方を変更できることだ。この柔軟性により、ロジックの内部ノードにアクセスすることが可能になる。「例えば、DDR3(Double-Data-Rate 3) SDRAMのI/FをFPGAに実装することで、そのI/Fを評価するのに十分なアクセシビリティが得られる。これはDDR3を評価するための数少ない手法の1つだ」とPrzybus氏は指摘する。FPGAによってコントローラの内部ノードを観測できるだけでなく、I/Fを介してデータパターンを印加し、トランザクションを開始して、実質的にプローブ不可能なシリアル伝送データのコピーを取り出すことが可能なのだ。

この手法を導入するには、FPGA内部に仮想的なロジックアナライザを構築する(検証チームがFPGAを再プログラムして挿入する)必要がある。それにより、チップの内部ノードをトリガー/トレースできるようになる。Przybus氏は、「基板上の信号を外部のテストヘッダーに接続するのではなく、FPGAにルーティングするのは良い方法だ」と述べている。

設計者が独自のロジックアナライザを設計したくなければ、FPGAベンダーが提供しているものを利用すればよい。例えば、Xilinx社は「ChipScope」によってその機能を提供している。

さらに、アクセシビリティを得るために、制御CPU自体をIPコアとしてFPGAに搭載することも可能だ。今日では、FPGAベンダーが提供する独自のRISC(縮小命令セットコンピュータ)コアも、業界標準のマイクロコントローラコアも、FPGAの容量をあまり気にせずに組み込めるほど小型になっている。FPGA内にCPUコアを配置することにより、ロジックアナライザ向けの制御ノードと、基板のそのほかの部分向けの検証/デバッグルーチンの両方を作成し、外部にホストコンピュータを用意することなく、検証/デバッグを行うことが可能になる。基板上にすでにFPGAが存在する場合には、明らかにこの方法が有用だ。検証/デバッグモード向けに再プログラムを行うことができ、基板に追加すべきハードウエアは最小限に抑えられるからである。

端子数の多いFPGAを使用して、それに入出力する信号を増やし、回路におけるFPGAの制御範囲を拡大したいと考える設計者は多いだろう。この機能性を考慮して、標準製品やASICで十分な設計にも、低コストのFPGAを採用する意味があると主張する人までいるほどだ。

アクセシビリティの高い設計を実現するには、検証/デバッグ技術者の要求を理解することが必須である。また、体系的な手法と経験豊かな設計者の見解を得ることが大いに役立つ。それによって、「いったいどうすれば信号を観測できるのだ」という、評価/解析技術者が繰り返し発する質問を回避することができるだろう。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- 「解読不可能」を破る量子コンピュータ――今から始める暗号セキュリティ

- Intelが「Core Series 3」モバイルプロセッサ、エッジ機器向けに

- フェライト(3) ―― 電子部品としてのフェライト

- アルミ電解コンデンサー(1)―― 原理と構造

- AI/HPC用ガラスビア向け 低収縮特性の銅ナノペースト

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- 次世代車載向けセキュリティコントローラー