監視回路を搭載する複合電源IC、産業用機器に組み込むSoC/FPGAに最適:ADI ADP5041

アナログ・デバイセズの「ADP5041」は、1.2A出力の降圧レギュレータを1チャネル、300mA出力のLDOレギュレータを2チャネルに加えて、監視回路を集積した複合電源ICである。SoCやFPGAの電源回路の部品コストや実装面積を低減できる。

アナログ・デバイセズは2012年1月、降圧スイッチングレギュレータとLDO(低ドロップアウト)レギュレータを集積した電源管理ICファミリの新製品として、電圧監視機能やウォッチドッグタイマーなどの監視回路を搭載する「ADP5041」を発表した。SoC(System on Chip)やFPGAといった複数の電圧入力が必要なICの電源回路を小型化できる。特に、「産業用機器分野の顧客の要求に応えて監視回路を搭載した」(同社)ことから、プロセスオートメーション機器をはじめとする産業用機器市場への展開を強化する計画だ。既に量産を開始している。1000個購入時の単価は1.79米ドル。

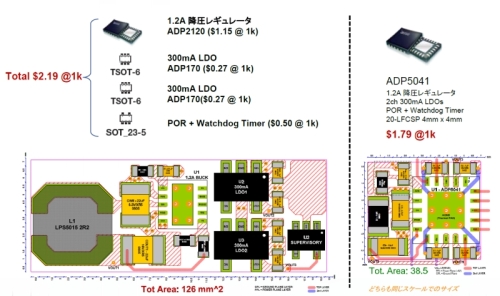

同社は、複合電源ICファミリとして、1.2A出力の降圧レギュレータと300mA出力のLDOレギュレータをそれぞれ2チャネル備える「ADP5034」などを展開している。今回発表したADP5041は、1.2A出力の降圧レギュレータが1チャネル、300mA出力のLDOレギュレータを2チャネル備える。ADP5034と比べて1チャネル減った降圧レギュレータに替えて、全温度範囲で±1.5%の精度を保証する電圧監視機能や、ウォッチドッグタイマー、マニュアルリセットのための入力インタフェースから成る監視回路を集積した。ADP5041を用いた電源回路は、降圧レギュレータ、2個のLDOレギュレータ、監視ICといった個別部品で構成したものと比較すると、ICのコストが約18%少ない1.79米ドル、実装面積は1/3以下の38.5mm2になるという(図1)。

降圧レギュレータのスイッチング周波数は3MHzと高いので、外付けのインダクタにチップタイプのものを使用できる。変換効率は最大で96%を実現した。LDOレギュレータは、容量が2.2μFの積層セラミックコンデンサで安定に動作可能である。電源電圧除去比(PSRR)は1〜10kHzの範囲で60dB、出力ノイズも60μVrms(標準値)に抑えた。

その他の主な仕様は以下の通り。降圧レギュレータは入力電圧範囲が2.3〜5.5Vで、出力電圧範囲が0.8V〜3.8V。出力電圧は外付けの抵抗分割回路を用いて調節できる。LDOレギュレータの入力電圧範囲は1.7〜5.5Vと低電圧側で広く、出力電圧範囲は0.8V〜5.2Vとなっている。ドロップアウト電圧は負荷が300mAのときで150mV。過電流保護、熱保護、ソフトスタート、低入力電圧保護機能を備える。パッケージは、外形寸法が4mm角の20端子LFCSPパッケージで提供される。

また、ADP5041と併せて、ADP5041から監視回路を省いた「ADP5040」も発表している。1000個購入時の単価は1.39米ドルである。

関連記事

昇降圧型コンバータの基本を知る

昇降圧型コンバータの基本を知る

昇降圧型コンバータは、現在、自動車のバッテリ関連の回路や、携帯機器、LED駆動回路などの幅広い用途に適用されつつある。本稿では、まず同コンバータの利用を検討すべき用途について説明する。その上で、同コンバータの各種実現方式や、代表的な製品の特徴について解説を加えることで、その有用性を明らかにする。- 最大入力電圧が20VのLDOレギュレータ、出力電圧雑音を15μVrmsに低減

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング