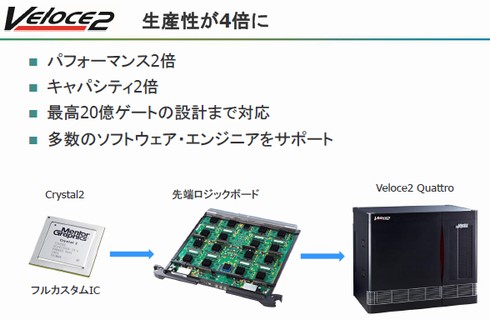

「生産性が4倍向上」、20億ゲートの回路を3MHzでエミュレーション可能に:Mentor Veloce2

Mentor Graphicsが大規模LSI開発の論理検証向けに投入したハードウェアエミュレータ「Veloce2」は、従来機種に比べてエミュレーションできる回路の規模とクロック周波数がともに2倍に高まった。消費電力と設置面積については従来機種と同等に抑えている。

Mentor Graphics(メンター・グラフィックス)は2012年4月、SoC(System on Chip)をはじめとする大規模LSIの開発に向けた論理検証用ハードウェアエミュレータの新機種「Veloce2」を発表した。検証可能な最大論理ゲート数(容量)は20億個と多く、エミュレーション時の実行速度(クロック速度)は最大3MHzと高い。いずれも同社従来機「Veloce」の2倍に達する。これらからVeloce2は、同社の従来機種に比べて「生産性を4倍に向上させた」(同社のEmulation DivisionでDirector of Marketingを務めるJim Kenney氏)と主張する。

Jim Kenney氏 Mentor GraphicsのEmulation Division、Director of Marketingを務める。半導体関連企業の首脳陣が集う報道関係者向けイベント「Globalpress Electronics Summit 2012」(米国カリフォルニア州のサンタクルーズで2012年4月23〜26日に開催)で、Veloce2を発表した。

Jim Kenney氏 Mentor GraphicsのEmulation Division、Director of Marketingを務める。半導体関連企業の首脳陣が集う報道関係者向けイベント「Globalpress Electronics Summit 2012」(米国カリフォルニア州のサンタクルーズで2012年4月23〜26日に開催)で、Veloce2を発表した。しかも、消費電力と設置面積については、それぞれ95kW(20億ゲート規模の回路を対象とする場合)、133×112cmと、いずれも従来機種と同等に抑えた。「最も近い競合他社機に比べて、取り扱えるゲート数当たりの消費電力は1/4、設置面積は1/3で済む。ユーザーの所有コストを引き下げることができ、5年間で50万米ドルに相当するコスト削減をもたらす」(同氏)という。

容量と実行速度を高められたのは、エミュレーション処理を担う同社のフルカスタムLSI「Crystal」を第2世代品に進化させたからだ。従来機種では90nmの半導体プロセス技術で製造した品種を使っていたが、今回の機種では65nm品「Crystal2」を用いている。

Crystal2で容量と速度が向上 65nm世代の半導体プロセス技術を適用し、フルカスタムのエミュレーション処理LSI「Crystal2」を新たに開発した。これを採用することで、エミュレータ装置の消費電力と設置面積を増大させることなく、容量と速度を向上させた。出典:メンター・グラフィックス・ジャパン

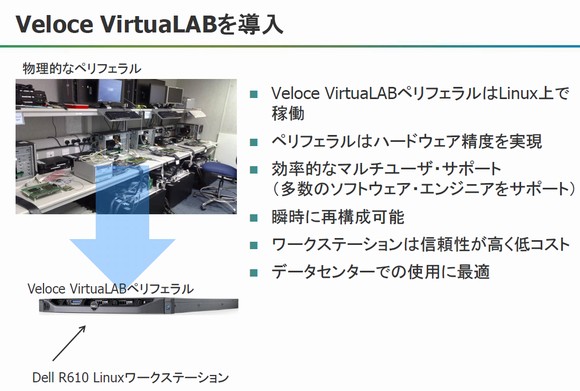

Crystal2で容量と速度が向上 65nm世代の半導体プロセス技術を適用し、フルカスタムのエミュレーション処理LSI「Crystal2」を新たに開発した。これを採用することで、エミュレータ装置の消費電力と設置面積を増大させることなく、容量と速度を向上させた。出典:メンター・グラフィックス・ジャパンMentorはこの他、外部ワークステーション上で稼働し、SoC検証ユーザーに「仮想ラボ」の環境を提供するツールソフトウェア「Veloce VirtuaLAB」も用意した。USBやEthernet、PCI Expressなど、実際のシステムで多く使われる周辺回路をあらかじめRTLでモデル化して備えている。これをVeloce2と連携させることで、「検証対象のハードウェアが最終的に使われることになる環境を、コンピュータ上で完全に再現できる」(同氏)という。

仮想ラボでシステム全体を検証 Veloce2と連携し、開発対象のチップに接続する周辺回路の動作をワークステーション上でエミュレーションする「Veloce VirtuaLAB」も提供する。開発対象のチップの試作前でも、システム全体の検証や組み込みソフトウェア開発を進められる(クリックで画像を拡大)。出典:メンター・グラフィックス・ジャパン

仮想ラボでシステム全体を検証 Veloce2と連携し、開発対象のチップに接続する周辺回路の動作をワークステーション上でエミュレーションする「Veloce VirtuaLAB」も提供する。開発対象のチップの試作前でも、システム全体の検証や組み込みソフトウェア開発を進められる(クリックで画像を拡大)。出典:メンター・グラフィックス・ジャパンVeloce2とVeloce VirtuaLABはともに既に供給を開始している。Mentorによれば、既に複数の顧客企業が採用しており、それら各社が開発するチップの量産に向けた妥当性検証フローに導入しているという。

Copyright © ITmedia, Inc. All Rights Reserved.