LVPECLの終端方法――低コスト、低消費電力の“Π型終端”“T型終端”:回路設計(1/4 ページ)

LVPECL(Low-Voltage Positive Emitter-Coupled Logic)の終端方法は、多くの選択肢の中から選ばなければなりません。ですが、選択のための明確な基準は存在しません。本稿では、LVPECLの終端回路の構成と外付け部品の値の決定方法について説明します。

はじめに

LVPECL(Low-Voltage Positive Emitter-Coupled Logic)は、周波数の高い信号向けに確立された差動出力の規格です。高速IC技術としては事実上、npn型のトランジスタしか存在しなかった1970年代以前から使用されているものです。アクティブに制御できるのはプル・アップ側(ハイ出力)だけで、プル・ダウン(ロー出力)を行うには外付けの受動部品が必要になります。

LVPECLに対応するドライバとレシーバをDC結合で接続する場合、外付け部品は、ドライバにバイアスをかける役割と、差動伝送路を終端する役割の両方を担います。これら2つの役割を果たせるようにするには、ドライバの出力部として柔軟性の高い回路を設計しなければなりません。このことが、LVPECLに慣れていない設計者に混乱をもたらすことがよくあります。設計者は、多くの終端方法の中からいずれかを選ばなければなりませんが、選択のための明確な基準は存在しません。

本稿では、LVPECLの終端回路の構成と外付け部品の値の決定方法について説明します。

まず、LVPECLに対応した出力ドライバの内部構造と、VCC−2V(VCCは電源電圧)の標準的なバイアス回路、終端回路について説明します。続いて、その標準的な終端方法の特徴と制約事項について詳細に述べるとともに、部品点数が少なく消費電力も少ない「π型終端」と「T型終端」という2つの終端方法について解説します。さらに、終端回路を内蔵するクロック・レシーバの使用法と、AC結合を利用する場合のカップリング・コンデンサと終端/バイアス用の抵抗の選択方法を紹介します。

LVPECLに対応した出力ドライバ

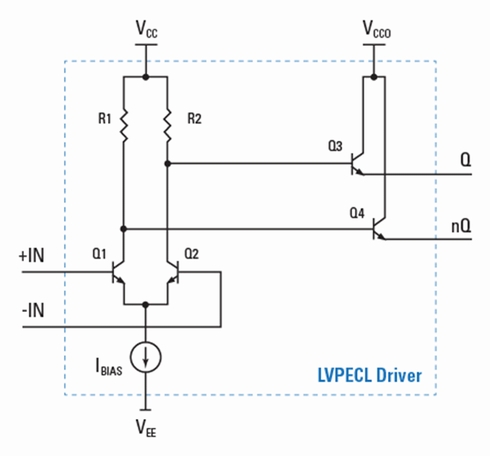

一般に、簡単なLVPECL回路は図1に示すようなオープン・エミッタ・ドライバ回路として実現されます。

図1から、以下の3つのことが分かります。

- 出力トランジスタがオンにならなければ、ドライバは何も出力しない。出力Q、nQが切り替わるには、それぞれに対してグラウンドへのDCパスが必要である。出力を使用しない場合には、Q、nQのピンをフローティングにして出力を確実にオフにすることにより、消費電力を最少化し、ノイズを低減することができる

- Q、nQのエミッタ電流の値は外付けのプル・ダウン抵抗の値によって決まる。抵抗値を変えることで、出力段の電源電圧VCCOの変動や、消費電力、ピーク・ツー・ピークの信号幅を調整することができる

- VCCOはVCCと同じ値にする。LVCMOS(Low Voltage CMOS)とは異なり、電源電圧の異なるレシーバ(クロック・レシーバ)に対応するためにVCCOをVCC以下にすることはできない。例えば、VCC=3.3V、VCCO=2.5Vとすると、出力トランジスタが飽和してスイッチング速度が大幅に低下してしまう

LVPECLの差動出力ドライバは、ギガヘルツ・レベルの周波数で動作します。そのため、適切な伝送路によってLVPECLレシーバと接続される必要があります。その際、回路設計者は、部品の配置のしやすさや、消費電力と性能のトレードオフに基づいて終端方法を選択することができます。ただし、配線長やビアも含めたシミュレーションによって、シグナル・インテグリティ(信号品質)について十分に検証する必要があります。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- フェライト(3) ―― 電子部品としてのフェライト

- 「解読不可能」を破る量子コンピュータ――今から始める暗号セキュリティ

- アルミ電解コンデンサー(1)―― 原理と構造

- Intelが「Core Series 3」モバイルプロセッサ、エッジ機器向けに

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- 次世代車載向けセキュリティコントローラー

- AI/HPC用ガラスビア向け 低収縮特性の銅ナノペースト

【図1】LVPECLを実現するオープン・エミッタ・ドライバの等価回路

【図1】LVPECLを実現するオープン・エミッタ・ドライバの等価回路