LVPECLの終端方法――低コスト、低消費電力の“Π型終端”“T型終端”:回路設計(3/4 ページ)

π型/T型のシャント終端

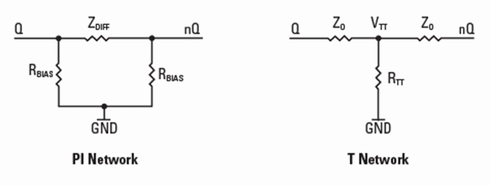

テブナン終端の短所は、図4に示すようなπ(別名Delta)型またはT(別名Y)型の抵抗回路を含む結合伝送路を使用することで解決/軽減できます。π型回路のコモン・モード・インピーダンスはRBIAS/2、T型回路の場合はZo/2+RTTとなります。また、結合伝送路の終端インピーダンスは、π型回路ではZDIFFで2×Zoに等しく、T型回路では2×Zoとなります。RTTの両端のコモン・モード電圧は、VTT=VCC−2.0Vに近いことからVTTと呼ばれています。

π型/T型の回路を使用することで、テブナン終端の5つの短所は、それぞれ以下のように解決されます。

(1)π型/T型回路を用いた終端では、ドライバの電流によって直接電力が供給される。そのため、テブナン終端で生じるバイアス用抵抗ストリングによる電力損失が発生しない

(2)コモン・モード・インピーダンスと負帰還により、表1に示すように、VCCOや温度の変動、デバイスの製造ばらつきに対してドライバの電流を打ち消すよう調整を行うことができる

(3)π型/T型回路は、コモン・モード電流のフィードバックによってエミッタ電流を制御する。例えば、RTT=50Ω、VCCO=3.3VのT型回路の場合、VCCOからVTTのポイントへのコモン・モード・フィードバックは66%(実際は出力トランジスタの動作点が異なるので、それより若干小さくなる)で、標準的な終端回路でフィード・フォワードされる60%よりも大きな値になる。2つの終端方法の差はそれほど大きくないようにも思えるが、トランジスタがローを出力する際、付加された50Ωのエミッタ抵抗における電圧降下が比較的小さいことを考慮すると、その差はかなり大きなものとなる

(4)2本の出力に対するバイアスと伝送路の終端に必要な抵抗が3個で済む。なお、どちらの回路でも、シャント終端を実現するために、QとnQの伝送路を結合する必要がある

(5)LVPECLに対応するレシーバの各入力端子に対して接続する抵抗の端子は1本で済む。そのため寄生容量も小さくなる

表1に、π型/T型終端において、VCCOの変動やデバイスの製造ばらつきを吸収するためにバイアス抵抗の値をどのように調整すればよいのかを示します。ここでは代表的なLVPECLに対応するクロックICとしてIDT社の「853S006」を例にとっています。このICのLVPECL出力については、工業温度範囲において論理値の0と1に対応する電圧の最大値と最小値が規定されています。VCCOが標準値のケース、VCCOが5%低下したケース、VCCOが5%低下し、なおかつプロセス的、温度的な要因でコモン・モード出力電圧が最小になるワースト・ケースの3つの場合について計算した結果が示されています。

| ケース | VCCO | Vout_h | Vout_l | Ibiasの最小値〔mA〕 | Ibiasの平均値〔mA〕 | Rbias | RTT |

|---|---|---|---|---|---|---|---|

| 標準値 | 3.3 | 2.350 | 1.650 | 2 | 10.9 | 183 | 67 |

| VCCOが5%低下 | 3.164 | 2.214 | 1.514 | 2 | 11.1 | 165 | 58 |

| VCCOが5%低下、プロセスがワースト・ケース、−40〜85℃ | 3.164 | 2.074 | 1.289 | 1 | 11.6 | 142 | 46 |

| 標準値 | 2.5 | 1.550 | 0.850 | 2 | 12.7 | 94 | 22 |

| VCCOが5%低下 | 2.375 | 1.425 | 0.725 | 1 | 11.9 | 91 | 20 |

| VCCOが5%低下、プロセスがワースト・ケース、−40〜85℃ | 2.375 | 1.285 | 0.500 | 0 | 14.0 | 64 | 7 |

| 【表1】クロック周波数と標準的なカップリング・コンデンサの値の関係 | |||||||

スイッチング速度は、ローを出力する際のバイアス電流の最小値によって決まります。この電流の値は、VCCOが5%低下する2つのケースでは、それを補うために比例的に少なくなります。バイアス抵抗については、徐々に低下する出力トランジスタのエミッタ電圧に対応するために、より値を小さくしなければなりません。そしてバイアス抵抗の値を下げることで、バイアス電流の平均値は増加します。逆に、バイアス電流の最小値を下げれば、バイアス電流の平均値も下がります。その効果は、VCCOが2.5Vの場合について、標準値のケースと5%低下したケースのバイアス電流を比較すれば見て取ることができます。

差動ペアのバイアス電流の平均値は、各ケースにおけるVCCOの値を用いて算出されます。いずれのケースにおいても、VCCOが5%上昇するとバイアス電流が増加します。設計者は、各ケースにおいて制限される抵抗値が、個々のアプリケーションの許容範囲に最適に収まるよう選択を行う必要があります。

π型の終端/結合伝送路

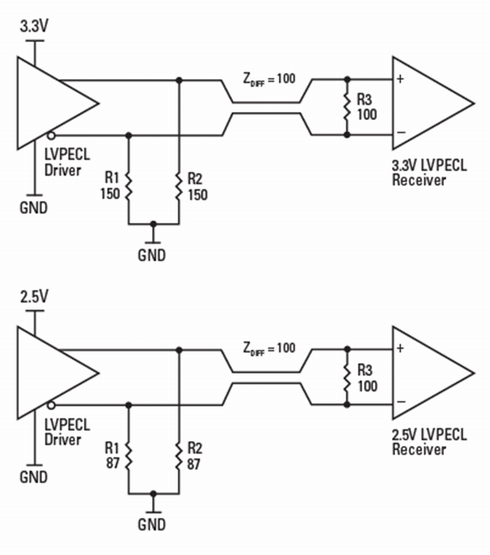

図4に示すπ型回路を結合伝送路に挿入した場合、ZDIFFは、ZDIFFで終端した結合伝送路と等しいインピーダンスに置き換えられます。この構成では、RBIASを使用するメリットを維持しつつ、ドライバのQ、nQのバイアス電流を個別に設定し、レシーバの端子に接続する抵抗の数を1個に抑えることができます。図5にそうしたπ型終端の具体的な構成例を示しました。

π型終端は、基板のレイアウトとして、BGAのように、単一のパッケージに対して複数のLVPECL信号を終端しなければならない場合に最も効果的な手法です。実際、レシーバ側ではLVDS(Low Voltage Differential Signaling)がもたらすのと同じメリットを享受することができます。Q、nQ出力には伝送路当たり1個のRBIASを接続するだけで済むので、プリント回路基板のLVPECLドライバ側に容易に配置することができ、シグナル・インテグリティの面でも優れているといえます。

なお、デバイスによっては、LVPECL信号の入力部に、「VT」といった名称のピンとしてコモン・モード・タップを設け、50Ωの差動終端抵抗を内部に組み込んでいるものがあります。このタイプのデバイスでπ型の終端を使用する場合には、VT端子はフローティングにしておきます。

T型の終端/結合伝送路

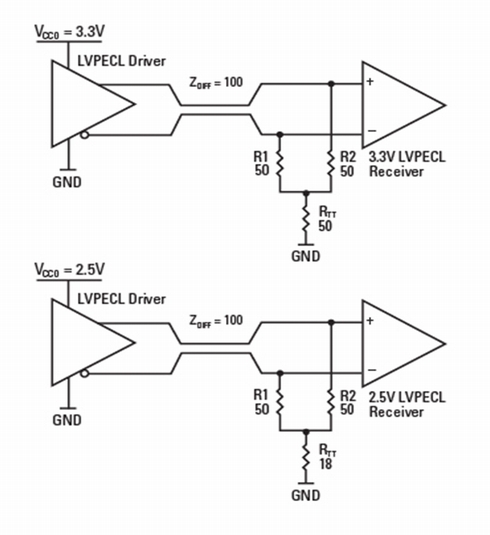

図4に示すT型の回路は、結合伝送路に挿入する場合にはLVPECLに対応するレシーバ側に配置します。レシーバの端子に接続される抵抗は1個だけです。RTTはコモン・モードのノードであるVTTに接続され、RTTに関連する寄生容量が差動モードのシグナル・インテグリティに影響を及ぼすことはありません。T型の終端は、例えば1:22のファンアウト・バッファなど、ファンアウトの大きいLVPECL対応デバイスに適しています。そうしたケースでは、恐らくπ型の終端における全てのプル・ダウン用バイアス抵抗をドライバ側に収めることは難しいでしょう。

図6に、T型回路の具体例を示します。なお、50Ωの差動終端抵抗とコモン・モード用のVTタップが組み込まれたLVPECL対応デバイスを使用する場合には、VTピンとグラウンドの間にRTTを接続します。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- フェライト(3) ―― 電子部品としてのフェライト

- 「解読不可能」を破る量子コンピュータ――今から始める暗号セキュリティ

- アルミ電解コンデンサー(1)―― 原理と構造

- Intelが「Core Series 3」モバイルプロセッサ、エッジ機器向けに

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- 次世代車載向けセキュリティコントローラー

- AI/HPC用ガラスビア向け 低収縮特性の銅ナノペースト

【図4】π型、T型の終端回路

【図4】π型、T型の終端回路 【図5】外付けのπ型終端回路(それぞれ3.3Vと2.5Vの電源電圧を使う例を示している)

【図5】外付けのπ型終端回路(それぞれ3.3Vと2.5Vの電源電圧を使う例を示している) 【図6】外付けのT型終端回路(それぞれ3.3Vと2.5Vの電源電圧を使う例を示している)

【図6】外付けのT型終端回路(それぞれ3.3Vと2.5Vの電源電圧を使う例を示している)