LVPECLの終端方法――低コスト、低消費電力の“Π型終端”“T型終端”:回路設計(2/4 ページ)

DC結合の場合の終端回路

まずはドライバ(クロック・ドライバ)とレシーバをDC結合する場合の終端回路について説明します。

標準的な終端回路

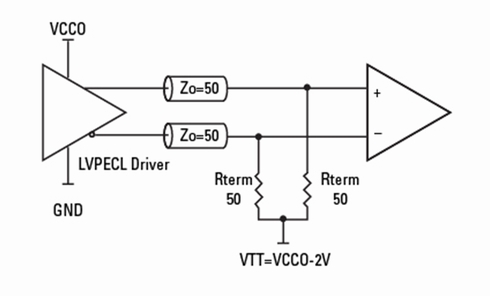

図2は、標準的なLVPECL終端回路です。図1を参考にすれば、終端電圧VTTの値は、トランジスタQ4の出力がロー(論理値の0)でエミッタ電流が2mAのとき、VCC(=VCCO)、抵抗R1、Q4のベース‐エミッタ間電圧Vbe、抵抗Rtermで構成される回路にキルヒホッフの法則を適用することで求められることがわかります。VTTは、同法則を満たすとともに、VCC(VCCO)に確実に到達できるように終端抵抗のコモン・ノードに設定された電圧の分岐点です。このVTTを設けることで得られるメリットは、ドライバの出力電流が電源電圧の変動の影響を受けなくなることです。これは、トランジスタにとって特にローを出力する際に重要なことです。トランジスタをカットオフから外れた状態に保持することで、デバイスのスイッチング速度を維持することが可能になります。一方、この終端方法の明らかな短所は、VCCO−2Vを生成するレギュレータが必要であることです。

テブナン等価回路による終端

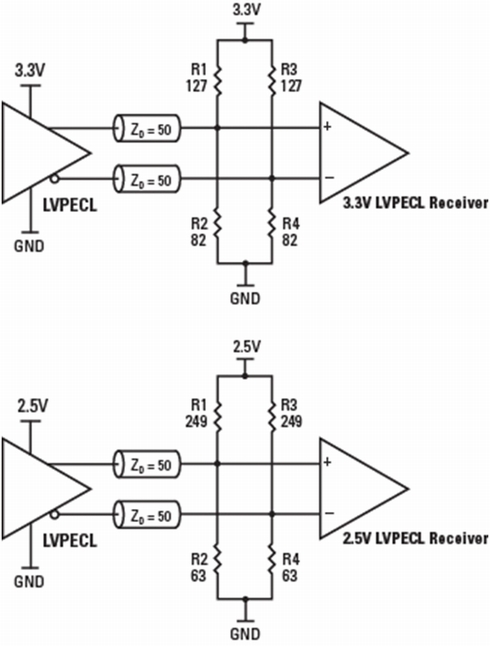

実際の終端回路では、図2のようなVTTは使用しないケースがほとんどです。その代わりに、図3のように2個の抵抗ストリングでバイアスするよう構成されたテブナン等価回路がよく使用されます。このテブナン終端では、抵抗ストリングによって各出力に対するVTTと50Ωの終端抵抗を同時に実現しています。QとnQを個別に終端することにより、分離された伝送路上でQとnQを異なるシングル・エンドの負荷に接続することも可能になります。

テブナン終端の短所としては、以下の5つが挙げられます。

(1)出力トランジスタのエミッタ電流による消費電力の他に、バイアス用の抵抗ストリングによる電力損失が生じる。その値は、電源電圧が3.3Vの場合、出力ペア当たり約80mWとなる

(2)自由度のない終端方法なので、VCCOや温度の変動、デバイスの製造ばらつきを吸収することができない

(3)VCCOの変動の一部は、バイアス用の分圧回路によって、VCCO=3.3Vの場合で39%、VCCO=2.5Vの場合で20%、テブナン等価回路のVTTにフィード・フォワードされる。そのため、特に出力がローである場合には、VTTを用いた標準的な終端方法と比べてエミッタ電流の制御が有効に働かない

(4)一般的な差動終端の場合、1つのVTTと2つの終端インピーダンス(50Ω)を実現するために必要な抵抗は3個で済む。テブナン終端ではそれよりも多くの抵抗が必要になる

(5)Q、nQの各信号に対し、LVPECLに対応するレシーバの端子にはそれぞれ2個の抵抗を接続することになる。それによって基板のレイアウトが複雑になる。また、抵抗が1個の場合よりも寄生容量が増えるため、性能が低下する

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- フェライト(3) ―― 電子部品としてのフェライト

- 「解読不可能」を破る量子コンピュータ――今から始める暗号セキュリティ

- アルミ電解コンデンサー(1)―― 原理と構造

- Intelが「Core Series 3」モバイルプロセッサ、エッジ機器向けに

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- 次世代車載向けセキュリティコントローラー

- AI/HPC用ガラスビア向け 低収縮特性の銅ナノペースト

【図2】LVPECL用の標準的な終端回路

【図2】LVPECL用の標準的な終端回路 【図3】テブナン終端(それぞれ3.3Vと2.5Vの電源電圧を使う例を示している)

【図3】テブナン終端(それぞれ3.3Vと2.5Vの電源電圧を使う例を示している)