FPGAの進化を上回れ! 生産5年目に突如現れた起動不良:Wired, Weird(2/4 ページ)

電源の異常か!?

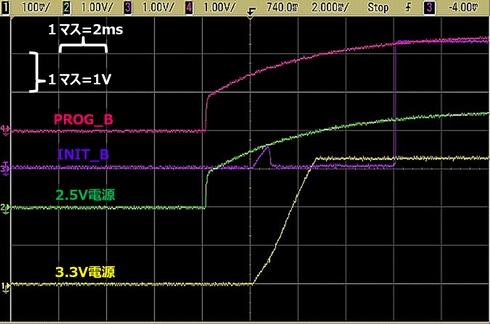

早速、FPGAの電源波形を確認した。図1に示す(赤色はFPGAのPROG_B信号、紫色はINIT_B信号、緑色は2.5V電源、黄色は3.3V電源の波形)。

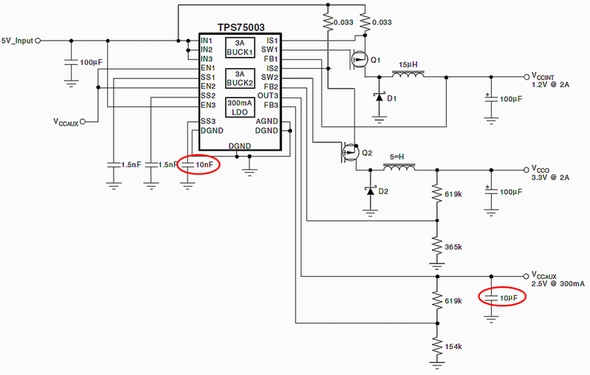

波形をよく観察すると、2.5V電源の立ち上がりが遅いことが分かる。2.5V電源はコンフィギュレーションを構成する時の電源で、FPGAがプログラムをPROMから取り込むために使用されていた。この電源波形は「正常な波形なのだろうか」と疑問に思って、基板の回路と電源ICの標準回路を比較した。電源ICメーカーの推奨の電源回路を図2に示す。なお、電源ICはテキサス・インスツルメンツ製の「TPS75003」を使用している。

2.5V電源はVccauxで、回路図を比較した結果、全く同じ回路で同じ定数が使用されていた。2.5V電源はレギュレータ(LDO)からの出力で、立ち上がり時間はSS3の10nFのコンデンサで制御され、出力コンデンサは10μF品が使用されていた(図2にそれぞれのコンデンサ部分を赤い丸で表示)。

図1では、2.5V電源の立ち上がりが、かなり鈍っているようにみえたが、果たして正常な動作波形なだろうか?

どうも2.5V電源が怪しい……

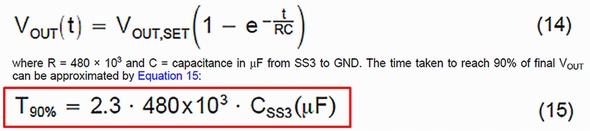

ということで、電源ICメーカーの技術サポートに問い合わせた。その結果、90%Vccaux(2.5V電源の90%電圧)の時間の計算方法を教えてもらった。図3にその計算方法を示す。

図3で赤く囲った「(15)」の式で電源の立ち上がり時間が計算できる。

計算すると……

CSS3=10nF ⇒ 0.01uF

2.3×480×103×0.01=11040us=11.04ms

と、おおよそ立ち上がり時間は11msという結果になった。

図1の実測では8ms程度であり測定誤差やコンデンサのバラつきを考えると妥当な値だった。この結果、電源回路の立ち上がりは問題ないと判断された。

Copyright © ITmedia, Inc. All Rights Reserved.