応答速度が高くリップルが低い包絡線検出回路:Design Ideas アナログ機能回路(2/2 ページ)

出力波形を比較

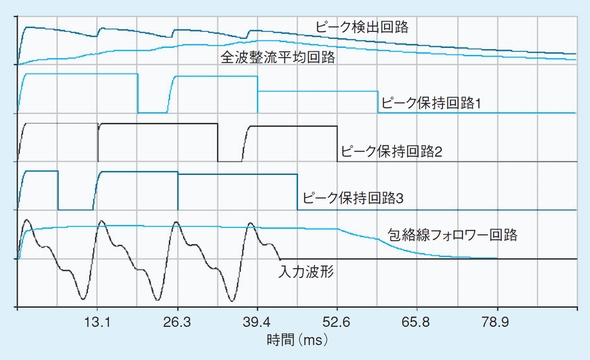

図2は、同様の時定数を備える全波整流平均回路とピーク検出回路に比べて、今回の回路のほうが優れていることを示したものだ。

図2:従来の回路と今回改善した包絡線フォロワー回路の出力波形を比較

図2:従来の回路と今回改善した包絡線フォロワー回路の出力波形を比較最も上の波形は、従来の回路の出力波形である。その下の3つが3段のピーク保持回路からの出力結果。最も下の波形が今回の包絡線フォロワー回路の出力結果を示したものだ。

図1におけるCMOSのシュミット・インバーターIC1は、リセット用クロック信号を生成する。コンデンサーC1と抵抗R1でクロック信号の周期を決定する。CMOSカウンターIC2は、連続してリセット信号を出力するリング・カウンターである。

ピーク保持回路にはリセット回路が付加されている古典的な構成を使った。抵抗R2とコンデンサーC2がリセット信号の立ち上がりエッジを微分する。このエッジでトランジスタQ1のベースが駆動される。直列抵抗R3はQ1がオンのとき、オペアンプから出力される過電流を防ぐ。抵抗R4と抵抗R5、コンデンサーC3、ダイオードD1は信号の減衰が通常よりも速いときに、出力をステップ変化させないようにするフィルター回路である。この構成が最小だ。

Design Ideas〜回路設計アイデア集

【アナログ機能回路】:フィルター回路や発振回路、センサー回路など

【パワー関連と電源】:ノイズの低減手法、保護回路など

【ディスプレイとドライバ】:LEDの制御、活用法など

【計測とテスト】:簡易テスターの設計例、旧式の計測装置の有効な活用法など

【信号源とパルス処理】:その他のユニークな回路

※本記事は、2008年7月29日にEDN Japan臨時増刊として発刊した「珠玉の電気回路200選」に掲載されたものです。著者の所属や社名、部品の品番などは掲載当時の情報ですので、あらかじめご了承ください。

「珠玉の電気回路200選」:EDN Japanの回路アイデア寄稿コラム「Design Ideas」を1冊にまとめたもの。2001〜2008年に掲載された記事の中から200本を厳選し、5つのカテゴリーに分けて収録した。

関連記事

過電流/過電圧保護用のブレーカー回路

過電流/過電圧保護用のブレーカー回路

今回は、少数の低価格な部品で構成されているが、電流/電圧のいずれかが設定条件を超えると的確に電源を遮断し、過電流/過電圧に対するブレーカーとして機能する回路を紹介する。 振幅制御機能を備えたGIC発振回路

振幅制御機能を備えたGIC発振回路

古典的なGIC(一般化インピーダンス変換器)に基づく回路である。固有の振幅安定化機能を備えた正弦波発振回路を紹介する。 1個のICでデバウンス対応のスイッチを構成

1個のICでデバウンス対応のスイッチを構成

今回は、低コストのプッシュボタン回路を紹介する。プッシュボタンスイッチを押すとワンショット回路が起動し、その出力によりトグルフリップフロップ(TFF)が起動してその出力レベルが反転する。これにより、デバウンスに対応済みのスイッチとして機能する仕組みだ。 入力インピーダンスの高いアンプの静電気保護

入力インピーダンスの高いアンプの静電気保護

オペアンプICはさまざまな半導体メーカーから供給されており、いずれも入力バイアス電流や入力オフセット電流が低く抑えられている。しかし、オペアンプ回路を計測用センサーにケーブル接続する際に発生するESD(静電気放電)の対策が難しい。今回は、その弱点を解決する回路を紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.