差動伝送路の設計(その2)、差動の結合と不要輻射:高速シリアル伝送技術講座(7)(1/5 ページ)

今回は、前回に引き続きLVDSを含む数Gビット/秒(bps)までの差動伝送路の設計と差動ペア間の結合の重要性、不要輻射ノイズなどについて説明していきます。

差動信号の伝送路設計(その2)

前回はLVDS物理層(PHY)製品とその差動伝送路の設計を説明していきました。LVDSは数百MHz〜3Gbps程度のアプリケーションに多く使用されていますが、高い周波数帯域では、プリント基板(PCB)やケーブル、コネクターの配線は単純な集中定数の信号線として扱うことができなくなります。そのため伝送路に含まれる各変化点のインピーダンスの整合と最適な終端が重要になります。

LVDSを含む差動伝送で、整合すべきは差動のインピーダンスです。差動インピーダンスに不整合があると信号の反射によるアイパターン(以下、EYE)の劣化や不要輻射ノイズにつながります。今回も差動伝送路設計で配慮すべき項目を引き続き説明していきます。これらを考慮し伝送路を設計することで追加コストも必要なく、シグナルインテグリティを向上させることができます。

PCB差動ラインの配線:Sのルール

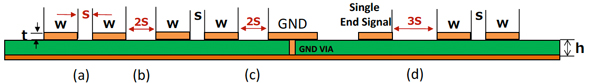

PCB差動信号の配線は図1のように配線幅Wと差動間隔Sを使用してレイアウトを行ないます。レイアウトの際、他の信号ラインからのクロストークによるノイズが少なくなるように検討しますが、他の差動ペアやシングルエンド信号、GNDガードパターンなどとの間隔の指針として、シンプルで分かりやすいSのルールがあるので以下に紹介します。

【Sのルール】

- 差動ペア間隔のSはPCB配線の最小値を使用し強い結合(密結合と言います)とします。(図1(a))

- 同じ層にレイアウトされる他の差動ペアとの距離は2S以上離します(図1(b))。

- ノイズガード用のGNDラインやGNDパターンからも同様に2S以上離してレイアウトします。(図1(c))

(GNDラインは共振を抑えるため1/4波長以下の間隔でGNDビアを打ちましょう。) - シングルエンド信号はGND層を挟んで別層にレイアウトすれば、クロストークノイズの影響を大幅に削減できます。差動ペアと同層にレイアウトする場合は、3S以上離します。(図1(d))

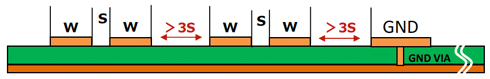

- 受信端でACゲインの高いCTLE(Continuous Time Linear Equalizer)注1)イコライザーを使用する場合は、イコライザーによってノイズも増幅されるため、図2のように他の差動ペアやGNDパターンからも3S以上離します。

差動ペア間隔Sを最小とした強い結合(密結合)の配線を採用すると、もう一つの優位点として、複数の差動ラインが同じ層にレイアウトされる場合に全体に占める差動信号配線の面積を減らすことができます。(10Gbpsを超えるようなアプリケーションでは、差動伝送路のインサーションロスを減らすために配線幅Wを太くし、差動ペア間隔Sを広げて差動ペア間の結合が弱いレイアウトも行なっています。詳細は今後のCMLの伝送路設計で説明していく予定です)

注1)CTLE(Continuous Time Linear Equalizer):伝送路のインサーションロスの逆特性を持たせ、補償するタイプのイコライザー、アナログイコライザー。

Copyright © ITmedia, Inc. All Rights Reserved.

図1:差動配線「Sのルール」

図1:差動配線「Sのルール」 図2:高ブーストCTLEイコライザー使用時のS

図2:高ブーストCTLEイコライザー使用時のS