差動伝送路の設計(その2)、差動の結合と不要輻射:高速シリアル伝送技術講座(7)(2/5 ページ)

差動伝送路の特性インピーダンスと平衡性、密結合

LVDSの差動インピーダンスは標準100Ωのため、差動伝送路の特性インピーダンスも100Ωで設計します。終端抵抗が内蔵されていないLVDSデバイスで長い伝送路を使用する場合、伝送路のインサーションロスを低減させるため低めのインピーダンス(90Ωなど)を採用し配線幅Wを太くする方法も可能です。

受信端の外付け終端抵抗の値は100Ω固定ではなく伝送路の特性インピーダンスに合わせ選択します。10%のインピーダンスミスマッチは5%の反射につながるため、使用するアプリケーションでインピーダンスミスマッチによる信号反射が許容できるかを検討し、受信端でのEYEの開口が十分かを確認します。

伝送路の特性インピーダンスと終端抵抗値に差があると、インサーションロスが少ない伝送路ではインピーダンスミスマッチによる反射が観測されますが、一般的にこの反射が次のサイクルまでに十分安定するのであれば、横軸方向のEYE開口への影響は少ないと考えられます。

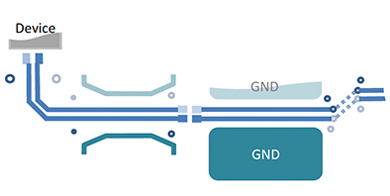

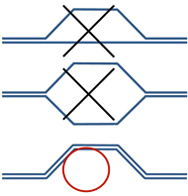

伝送路中の差動インピーダンスの不連続点が最小になるように伝送路はなるべくシンプルに設計します。配線上の制限で配線とその近傍に不連続がある場合、差動の片方の各変化点(キャパシターや抵抗との接続部、曲げ、ビア、デバイスピン、コネクター)に行った処理は図3の薄い色の鏡に映したように、もう片方にも平等に処理を行い、平衡性を維持します。

差動配線の近傍で不連続が起こる部分では、両側に同じく不連続にします。従うべきは「平衡」です。その際、図4のように差動ペアの結合を乱さないようにレイアウトを行います。

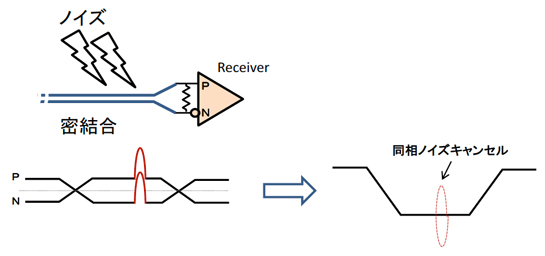

不要輻射低減には平衡性も重要です。差動ペア間を密結合にすると不要輻射も低減し、外来ノイズにも強くなります。

ノイズが印加された場合、Sが狭いと差動のP(Positive)とN(Negative)双方に同じノイズが重畳されるためレシーバーでキャンセル可能となります。ノイズが重畳された場合も考慮し、レシーバーでコモンモードノイズとして処理できるよう差動ペアの間隔Sはできるだけ狭くします(図5)。

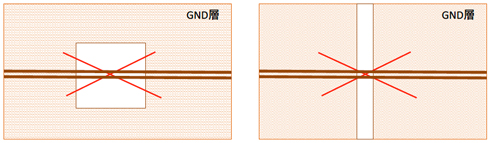

PCB上の差動配線では、差動ペア間の結合(差動モードインピーダンス)は、リファレンスとなる下層GNDとの結合(コモンモードインピーダンス)も関係しインピーダンス整合を取っているため、図6のように信号配線下のリファレンスのGND層を抜いたり、スリットを入れたりしてはいけません。

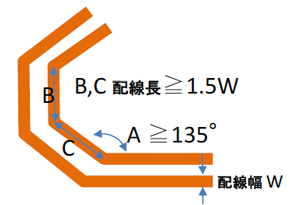

差動配線の方向を変える場合、インピーダンスの不連続となるため90度曲げ配線は使用せず、円弧か緩やかな(180-45)度や(180-30)度配線を繰り返し、折り曲げます(図7)。

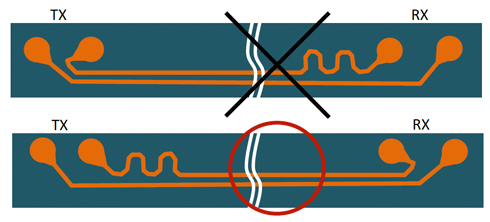

差動ペアの配線長を合わせるため、差動の結合が送信側ピンもしくは受信側ピンのどちらかが崩れる場合、受信側は極力崩さず、図8下側の密結合のまま配線することで、受信端でのインピーダンスミスマッチによる波形の乱れを抑えることができます。

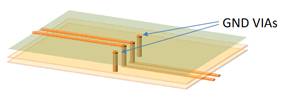

差動伝送路は信号品質の低下を防ぐため、できるだけ表層のみで配線できるよう最優先でレイアウトを行います。しかし別層へ移動させなければならない場合は、図9のように差動信号ビアの近くに結合先のGNDビアを2本配置し、信号ビア部分でのインピーダンスの上昇を防止します。

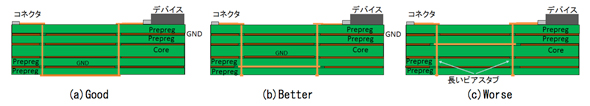

差動伝送路の層間移動が必要な場合、移動回数を最小限とし反射の原因となる信号ビアの数を減らすことに注力しましょう。図10(c)のような内層へのストリップライン配線では、ビアスタブ注2)を削るバックドリルやビルドアップ構造でない場合、余分な配線部分となるスタブ配線が残ります。そのため、ビアのスタブ長が常に最短となるよう図10(a)や(b)のように、層間の移動では信号元から一番離れた層を選び配線を行います。

内層への配線では内層ストリップラインを表層のマイクロストリップラインと同じ配線幅Wにすると、コモンモードの結合先となる上下電源層との結合が強いため特性インピーダンスが大幅に低下するので注意が必要です。そのため内層のストリップラインは個別に配線幅Wを調整し、差動のインピーダンス整合を行います。

また配線レイアウトでは以下の点にも注意します。

- コネクターを使用する場合、I/Oデバイスはコネクター付近に実装します。

- 4層もしくはそれ以上の多層基板を使用します。

- テストポイントなどを高速差動信号配線上に配置しない。

- クロック系信号やスイッチングレギュレーターの近傍に高速差動配線を引かない。

- 速度が異なる差動ラインがある場合、より高速なラインを優先し配線を行います。

- 切れ目のないリファレンスのGND層を下層に配置し、表層で差動ラインを配線します。

- 十分な差動ペアの結合のためS<Wとします。

- 特性インピーダンスを固定するため、各層での差動配線幅Wは常に一定とします。

- 差動ペア間スキュー(イントラスキュー)を最小とするため、電気長(≠物理長)をそろえるか、ペア間隔Sが最小の密結合の配線とします。

注2)スタブ:PCB上でパターンが途中で途切れ、開放端になったもの。

Copyright © ITmedia, Inc. All Rights Reserved.

左=図3:差動配線 平衡性の維持 / 右=図4:差動ペアの密結合を維持

左=図3:差動配線 平衡性の維持 / 右=図4:差動ペアの密結合を維持 図5:差動ペア間Sが小さい場合のノイズ重畳

図5:差動ペア間Sが小さい場合のノイズ重畳 図6:差動配線とリファレンスGND層

図6:差動配線とリファレンスGND層 図7:差動配線の曲げルール

図7:差動配線の曲げルール 図8:受信端差動配線。密結合の維持(下側)

図8:受信端差動配線。密結合の維持(下側) 図9:差動ビアと結合先のGNDビアの配置

図9:差動ビアと結合先のGNDビアの配置 図10:信号の層間移動

図10:信号の層間移動