差動伝送路の設計(その2)、差動の結合と不要輻射:高速シリアル伝送技術講座(7)(3/5 ページ)

終端について

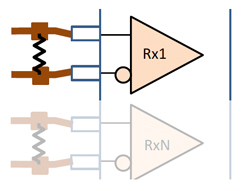

設計した差動の特性インピーダンスに合わせた抵抗値で終端し、インピーダンス整合を取ります。100Ω固定といった決まりはありません。ただしデバイスに終端抵抗が内蔵されたデバイスの場合、終端抵抗値は変更できないので、伝送路の特性インピーダンスの設計はデバイス内蔵の終端抵抗値にあわせます。LVDSではドライバは電流源駆動、レシーバーは電圧を検出し動作しています。そのため受信端に終端抵抗のない状態では使用できません。LVDSの終端抵抗器は受信側デバイスのP(Positive)とN(Negative)ピンにまたぐようにピンから最短で配置します(図11)。

終端器は精度1%の小型表面実装タイプの抵抗を使用し、デバイスピンと終端抵抗の距離は最短とします。使用する帯域にもよりますが、距離は7mm以下としましょう。

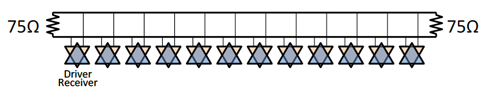

M-LVDSのマルチドロップやバス構成の場合、ぶら下がるノード数に依存し、実効インピーダンスが大きく低下します。そのため図12のように終端部の抵抗値は最大負荷時のインピーダンスに合わせた値を選択します。

シングルエンド信号と差動信号の電磁放射エネルギー

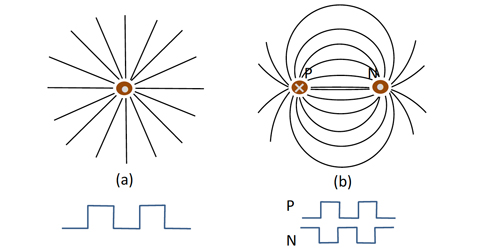

同軸やシングルエンドのマイクロストリップラインはTEM波や準TEM波で遠方に信号を伝達していますが、差動伝送ラインでもP(Positive)とN(Negative)が密結合し準TEM波で信号が伝わっていきます。TEM波は連載第5回で説明したように、電界と磁界が直交しながらエネルギーが伝搬していきますが、放射されるノイズのエネルギーも遠方に到達します。

図13は伝送路の断面図で、伝送路から放射されるエネルギーを電気力線で表現しています。図13(a)の配線1本では電気力線の結合先がないため、ほとんど全ての電磁エネルギーが外部へ放射されます。図13(b)の差動配線では差動ペアのPとNが結合し、外部へ放射される電気力線が大幅に少なくなります。

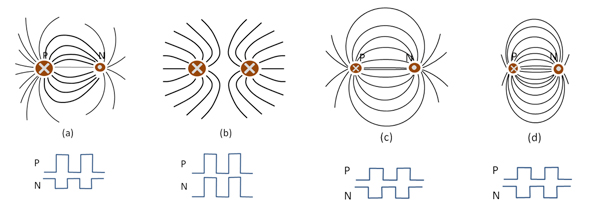

差動配線でもドライバ側が駆動するPとNの電流がアンバランスであったり、PCB上の配線の太さが違ったりすると図14(a)のように外部に放射される電気力線が多くなり、放射ノイズが大きくなります。

またこの差動配線に2本のシングルエンドの同相信号を流した場合、図14(b)のように反発し合い、放射されるノイズは大きくなります。デバイスのPとNの差動出力に電源からのコモンモードノイズが重畳された場合がこれに相当し、エネルギーの一部が不要輻射ノイズとして放射されます。

差動ドライバからのバランスのとれたP(Positive)とN(Negative)出力と、差動伝送路のPとNペアが平衡して近接する密結合の差動配線では図14(d)のように電磁気的にペアが強く結合するため、電気力線が閉ざされ、図14(c)よりも外部へ放射されるエネルギーが小さくなります。PとNの距離が近いほど結合が強く外部に放射されるノイズは減少します。

Copyright © ITmedia, Inc. All Rights Reserved.

図11:終端抵抗器の位置

図11:終端抵抗器の位置 図12:M-LVDS。バス構成時の両終端とその抵抗値

図12:M-LVDS。バス構成時の両終端とその抵抗値 図13:(a)シングルエンド配線、(b)P/N差動配線 ※放射エネルギーを電気力線で表示

図13:(a)シングルエンド配線、(b)P/N差動配線 ※放射エネルギーを電気力線で表示 図14:(a)差動のアンバランス、(b)同相信号、(c)バランスのとれた結合、(d)密結合

図14:(a)差動のアンバランス、(b)同相信号、(c)バランスのとれた結合、(d)密結合