電源ノイズがデルタ-シグマADCに与える影響の理解:アナログ設計のきほん【ADCとノイズ】(11)(3/3 ページ)

ADCの電源それぞれのノイズがシステム性能に与える影響

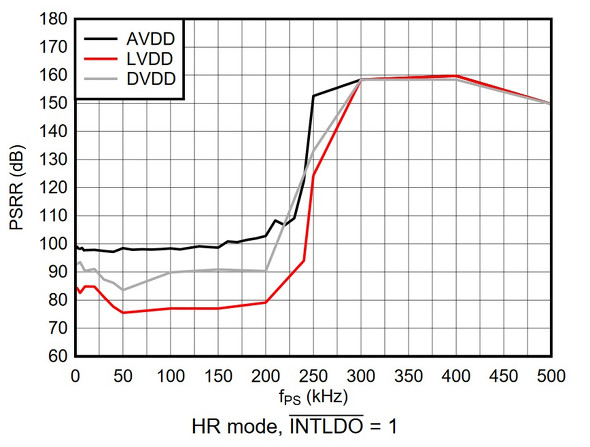

前のセクションでは、アナログ電源を例にして電源ノイズを測定、規定する方法を説明しました。電源電圧が1つで十分なADCには、この方法でも容認できるかもしれませんが、高分解能ADCでは最低でもアナログ電源とデジタル電源が別々になっている傾向があり、一部の高精度ADCにはさらに多数の電源が必要になります。例えば図5から、ADS127L01には、実はアナログ(AVDD)、デジタル(DVDD)および、低電圧変調回路電源(LVDD)という3つの電源があるのが分かります。図9は、周波数に対する各電源のPSRRのプロット図です。

図9から、ADS127L01の電源ノイズの影響を最も受けやすいのはLVDDだという結論を導けます。この電源を直接使用するのが、入力信号をサンプリングするADCのデルタシグマ変調回路であるため、このことは直観的に納得できます。であれば、このADCで最大限の性能を得るためには、LVDDのノイズが最小限になるように、LVDDに対して電源ノイズを低減する手法を適用するとよいでしょう。

さらに、図9からは、電源周波数(fPS)が約200kHzになるまでは、3つすべての電源のPSRRが相対的に一定であることが分かります。約200kHzになると、3つすべての電源でPSRRが160dBまで増加し始めます。図9では、ADS127L01はワイドバンド1デジタルフィルターを使用し、512kSPSで動作しています。このフィルターレスポンスにより、ADCの通過帯域は約204kHzに設定されます。したがって、ADS127L01のデジタルフィルターの遮断帯域減衰レベルにより、ADC通過帯域を超えた周波数の電源リップルが、さらに約116dB除去されます。これにより、3つすべての電源で高周波数のPSRRが改善します。

図9を深く読み込むことで、電源ノイズに関する2つの重要な疑問へのヒントが得られます。1つ目は、システムのPSRを考えるときに最も問題となるのはどのADC電源か、2つ目は、システムの電源ノイズ全体を低減する方法は何か、ということです。

本連載の最終回になる次回は、ADS127L01評価モジュールを使用する実際例を用いてこれらの疑問に答えながら、電源ノイズについて引き続き説明します。

著者紹介

ブライアン・リゾン(Bryan Lizon)

テキサス・インスツルメンツ 高精度ADC製品プロダクト・マーケティング・エンジニア

関連記事

高分解能ΔΣADC回路のリファレンスノイズ低減

高分解能ΔΣADC回路のリファレンスノイズ低減

システム全体でリファレンスノイズのレベルに与えるゲインの影響を低減するための方法をいくつか分析し、リファレンスノイズについての説明をまとめていきます。低分解能ADCと高分解能ADCに対するリファレンスノイズの影響の違いも考察します。 デルタ−シグマADCでの電圧リファレンスノイズの影響

デルタ−シグマADCでの電圧リファレンスノイズの影響

さまざまなノイズ源が高精度デルタ−シグマADCに与える影響をより深く理解するために、電圧リファレンスノイズについて取り上げます。 信号の分解:デルタ-シグマADCでのアンプ・ノイズの影響

信号の分解:デルタ-シグマADCでのアンプ・ノイズの影響

今回と次回は、アンプのノイズがデルタ-シグマA/Dコンバーター(ADC)に与える影響について考察します。まずは、「出力換算ノイズと入力換算ノイズ」「ADCの入力にアンプを追加」「低分解能ADCと高分解能ADCの比較」について扱います。 高精度デルタ-シグマADCの 有効ノイズ帯域幅(ENBW)の理解【算出方法】

高精度デルタ-シグマADCの 有効ノイズ帯域幅(ENBW)の理解【算出方法】

今回は、「ENBWの算出方法」「システム変更がENBWに与える影響」について、2段フィルターを使用したシンプルな例を説明しながら、デルタ-シグマA/Dコンバーター(ADC)やシステムレベルの設計と絡めて考察していきます。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

図9:TA=25℃、AVDD=3.3V、VREF=2.5V、HRモード、¯INTLDO¯=1

図9:TA=25℃、AVDD=3.3V、VREF=2.5V、HRモード、¯INTLDO¯=1