ダイナミック回路とスタティック回路の内部構成と仕組み:Q&Aで学ぶマイコン講座(89)(2/4 ページ)

ダイナミック回路とスタティック回路

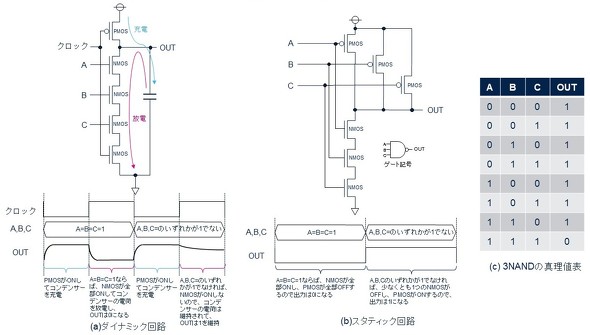

図2に、もう少し複雑な構造の3NANDゲートの例を示します。動作原理は図1で示したインバーターと同じです。

ダイナミック回路では、クロックがロー期間にコンデンサーを充電し、ハイ期間にデータを確定させます。この時のコンデンサーは、寄生容量または専用に設けたコンデンサーです。配線の持つ寄生容量で十分データを保持できるならば、専用のコンデンサーは不要です。多くの場合、配線の寄生容量で十分ですが、設計時にシミュレーションをして確認します。不十分であれば、専用のコンデンサーを設けます。

3NANDゲートであるため、入力は3つあります。その3つが全て1の場合にNMOSが全てONして、クロックがハイになった時にコンデンサーの電荷を放電し、OUTを0にします。3つの入力のどれか1つでも0であれば、その入力のNMOSがONしないため、コンデンサーの電荷は維持されてOUTは1になります。

スタティック回路の場合、3つの入力が全て1であれば、全てのNMOSがONし、全てのPMOSはOFFするためOUTは0になります。3つのいずれかが0であれば、少なくとも1つのNMOSがOFFし、PMOSがONするためOUTは1になります。この場合、必ずPMOSかNMOSのどちらかが、OUTをドライブします。

ダイナミック回路もスタティック回路も、1クロック周期でデータを確定するため、演算の実行サイクルは同じです。

ここで、使用されているMOSの数に着目してください。ダイナミック回路の場合、PMOSは1つでNMOSは入力信号数とクロックになります。入力信号数をnとすると、MOSの総数は(n+2)個です。スタティック回路の場合は、クロック分のMOSは不要ですが、PMOSもNMOSもn個必要なので、(2n)個のMOSが必要になります。nが3以上だとダイナミック回路の方が使用するMOSの数は少なくて済み、回路面積も小さくなります。

ただし、回路面積を小さくできるからといって、ダイナミック回路の方が優れているということはありません。それぞれメリット/デメリットがあるため、次の章でそれぞれ解説します。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング