マイクロプロセッサを使用したシステム、基板レイアウト作成時の重要ポイントは:マイクロプロセッサQ&Aハンドブック(4)(3/6 ページ)

» 2024年12月19日 10時00分 公開

[小谷豊(STマイクロエレクトロニクス),EDN Japan]

基板の層構成

ここでは、基板のプリプレグと銅箔の厚みおよび、配線層の割当てを決めます。

この時、よく聞かれる質問&その回答として以下のようなものがあります。

Q1 DDRメモリとプロセッサを基板のトップ側に配置した時、DDRメモリの高速信号はどのレイヤーに配置すべきでしょうか?また、高速信号とペアになるGNDはどこに配置すべきでしょうか?

A1 配線のレイヤーを変えるためにビアを通ると、インピーダンスが不連続な箇所が生まれます。そのため、インピーダンスマッチングが重要な配線はトップの銅箔に配置するのがベストです。

Q2 基板のプリプレグの厚みは、薄くする/厚くする、どちらがよいのでしょうか?

A2 基板のプリプレグの厚みは、薄い方が高密度な配線設計をしやすいです。

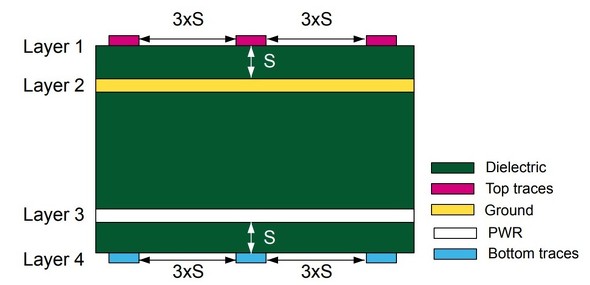

基板配線で特に重要なのは、高速なDDRメモリの信号です。中でも、シングルエンドの配線はそれぞれの配線を離して、クロストークの発生を抑える必要があります。どれだけ配線を離すかは、S-3S分離ルールに従います(図1)

図1:S-3S分離ルール [クリックで拡大]

図1:S-3S分離ルール [クリックで拡大]アプリケーションノート: AN5692 DDR memory routing guidelines for STM32MP13x product lines Figure 6. S-3S isolation rule illustration

基板のプリプレグの厚みをSとした場合、隣り合う配線はSの3倍離す必要があります。BGAのボール付近ではこのS-3S分離ルールを守れない状況が発生しますが、この際もできるだけ、Sの2倍以上の配線トラック間隔を確保するようにします。このS-3S分離ルールを守りつつ、高密度な配線を実現するために配線間隔を小さくしようとすると、高速信号とGND間の距離をなるべく短くすること、つまりトップのプリプレグの厚みを薄くすることが重要になります。また、プリプレグの厚みは基板製造メーカーが採用しているプリプレグの材質によって異なります。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentPR

Pickup ContentsPR

Special SitePR

あなたにおすすめの記事PR