ターミネータII:Signal Integrity

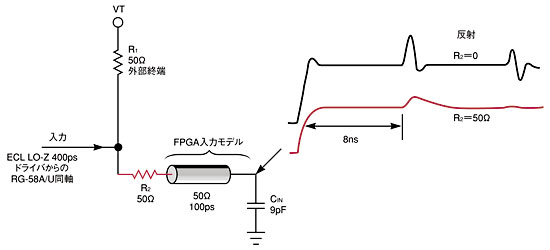

前回のコラムでは、信号品質に対する要求が非常に厳しい、やや問題のあるシステムアーキテクチャを示した。信号源は、立ち上がり時間が400psの低インピーダンスECLドライバを使い、3フィート(約0.9m)のRG58A/U同軸ケーブルで受信回路に接続されている。

信号源は他の誰かが作成したものなので、低インピーダンスECL出力を変更することはできない。また政府機関の契約により、在庫にあるFPGAと50Ω±1%の外部終端抵抗を使って、受信回路を設計しなければならないことになっている。

以上の条件から、50Ω終端を使えばうまくいきそうだが、残念なことに、FPGAには9pFの入力容量がある(図1)。R2=0Ωとして、これを直接50Ωの外部終端抵抗に接続すると、入力容量は終端の動作に干渉し、大きな反射を起こす。反射は、同軸ケーブルの往復遅延に相当する8nsごとに返ってくる。

この回路のインピーダンスを定量化すると、400psの立ち上がり時間はおよそF=0.35/(400ps)=875MHzの周波数に相当する。この周波数では、FPGA入力の9pFの容量によるインピーダンス振幅(1/(2πFCIN))はわずか20Ωである。この低いインピーダンスが50Ω終端の負荷となり、終端の役割を妨げるのだ。

ここで、50Ωの抵抗R2をFPGA入力と直列に挿入してみよう。これにより、FPGAの実効入力インピーダンスは、少なくとも50Ω以上となる。最悪の場合で、コンデンサのインピーダンスが完全にゼロとしても、並列になっているR1とR2により、終端のインピーダンスは25Ωとなり、反射係数は1/3を超えることはない。

抵抗R2は分離用の部品として動作し、FPGAの入力容量が直接終端抵抗に負荷をかけるのを防ぐ。この回路ではR2を50Ωとすることにより、反射信号の振幅は1/4に減少する。

同時に抵抗R2は、受信信号の立ち上がり時間を鈍らせてしまう。これは、R2とCINの組み合わせが、RCローパスフィルタとして動作するためである。この回路では、R2を50Ωとすると、信号の立ち上がり時間は2倍になる。

また、遅延した反射により、後続のエッジのタイミングが実際とずれてしまうことを心配されるかもしれないが、発生するジッターは、反射信号の振幅(元の信号振幅に対する割合で表したもの)に信号の立ち上がり時間を乗じたものに比例する。反射が1/4に減少し、立ち上がり時間が2倍に増加するならば、ジッターは1/2に減少できることになる。この結果はまずまずだが、もう少し改良を加えたいと思う。

次回のコラムでは、受信信号の立ち上がり時間をできるだけ鈍らせることなく、終端インピーダンスを正確に50Ωにする方法を示す。

<筆者紹介>

Howard Johnson

Howard Johnson氏はSignal Consultingの学術博士。Oxford大学などで、デジタル・エンジニアを対象にしたテクニカル・ワークショップを頻繁に開催している。ご意見は次のアドレスまで。www.sigcon.comまたはhowie03@sigcon.com。

Copyright © ITmedia, Inc. All Rights Reserved.

図1 50Ωの抵抗R2を追加することで、終端のインピーダンスが上がり、反射が減少する。しかし、信号の立ち上がり時間が遅れる。

図1 50Ωの抵抗R2を追加することで、終端のインピーダンスが上がり、反射が減少する。しかし、信号の立ち上がり時間が遅れる。