積層CSP設計のコツ(3/3 ページ)

コストは最小限、生産性は最大限に

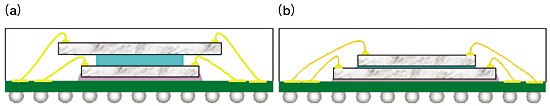

チップを積層する際に考慮すべき問題の1つに、異なる大きさの複数のチップをどのような順番で重ねるかというものがある。同一サイズのチップの積層では、チップ間にスペーサを配置することで、基板のフィンガーと下層のチップのパッドを接続することができる。この方法が利用できる場合に、それを用いて小さいチップを下層に置くのか、それともその方法は使わず、小さいチップを上層に置くのかということである。小さいチップのほうに、性能上の厳しい要件がある場合には、ワイヤーを短くするために、前者の方法を用いるほうがよい(図4)。

積層CSPを用いる目的は、部品点数、セットの基板面積、さらにはコストを低減することである。エンドユーザーにとっては、積層CSPなどの手法を用いて、より集積度の高いパッケージを作ることにより、製品の小型化とコストの低減が実現されることが望ましい。

しかし、積層CSPは本質的にはコストが高くつく手法である。組み立て歩留りに起因するコスト、物流コスト、材料費など、積層CSPは必ずしもコスト面では有利ではない。従って、最終的な製品が正しく動作し、信頼性も高いことはもちろんだが、積層CSPならではのコストの増加要因には十分に注意する必要がある。

積層CSPでは、組み立て歩留りがコストパフォーマンスを評価する際の重要な要素の1つだといえる。しかし、その他の要素も総コストに大きな影響を与える。そうした要素は、生産性を重視した設計の考え方に密接に関係する。もちろん、パッケージの主要部品もそうした要素に含まれる。

積層CSPは、無線通信アプリケーションや携帯機器のアプリケーションでよく使用される。そうしたアプリケーションへのとどまることのない低コスト化/小型化の要求に対応して、ここ数年の間に積層CSPの技術は著しく進歩した。単一のチップのパッケージ設計ではフィンガーピッチの改善が目標となり、チップ設計ではパッドピッチを改善してきた。I/O数が増加する一方でパッケージ基板の面積は縮小しなければならないという状況の中、基板に関するパラメータはいずれも向上した。そのパラメータとは、金属配線そのものとその間隔、ビア半径とパッドのサイズ、基板の厚さ、マルチレイヤー技術、金属めっき技術、はんだマスク技術などである。

積層CSPでは、硬い基板を用いると、いくつかの要因から高度な技術の利用が必要となり、最終的に基板コストが増大してしまう。そうした設計上の考慮点とコストのトレードオフについてよく検討することにより、積層CSPでも、単一チップの場合のコストに近づけることが可能になる。一般に、積層CSPの基板は、個々のチップに対応して設計しなければならず、最上層の配線密度が高くなる。積層する各チップを協調設計することにより、この配線密度の増加を抑えることができる。いささか極端な例を挙げると、2つのチップのすべての同一信号をチップ間でワイヤーボンディングできれば、2つのチップを接続するために基板を使用する必要はなくなる。このようなアプローチで設計上の問題点を解消することにより、コストを最小限に抑え、生産性を高めることが可能になる。

積層するチップ間の信号を直接ボンディングするのが困難な場合、1つのチップから他方のチップへ信号を中継するためのフィンガーを追加する必要がある。フィンガー密度が増加すると、基板コストが増加する。また、ワイヤー径を細くする方法を採用した場合、単位長当たりの抵抗値が大きくなるため、ワイヤー長の制約が厳しくなる。さらに、フィンガーを複数列にすることが難しい場合は、フィンガーのピッチが小さくなるため、ワイヤー径、ワイヤー長、ワイヤーの電気的影響について考慮しなければならない。

チップ積層の順序

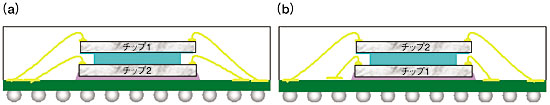

ほぼ同じ大きさの2つのチップを積層する場合は、下のチップのワイヤーと上のチップの間に干渉が生じないようにスペーサを使用する必要がある。このとき、ワイヤー量が非常に多い方のチップを下層に配置し、それに関連するフィンガーを内側の列に配置すると、フィンガーのピッチは小さくなる。一方、ワイヤー量が非常に少ないチップを下層に配置すると、ワイヤーが密集するチップのフィンガーが外側の列になるため、フィンガーのピッチが大きくなり、望ましい配置が可能となる(図5)。

Copyright © ITmedia, Inc. All Rights Reserved.

図4 チップの大きさが異なる場合の積層方法 小さいほうのチップの性能が重要な場合は、スペーサを用いて小さいほうを下層に置く(a)ほうが、上層に置く(b)よりも性能が得やすい。

図4 チップの大きさが異なる場合の積層方法 小さいほうのチップの性能が重要な場合は、スペーサを用いて小さいほうを下層に置く(a)ほうが、上層に置く(b)よりも性能が得やすい。 図5 チップの大きさが同じ場合の積層方法 チップ1のワイヤー量はチップ2よりもかなり少ない。チップ2を下層に配置するフィンガーのピッチは小さくなる(a)が、チップ1を下層に配置するとフィンガーのピッチは大きくなる(b)。

図5 チップの大きさが同じ場合の積層方法 チップ1のワイヤー量はチップ2よりもかなり少ない。チップ2を下層に配置するフィンガーのピッチは小さくなる(a)が、チップ1を下層に配置するとフィンガーのピッチは大きくなる(b)。