変化するDFM市場(3/5 ページ)

TSMC社のリファレンスフロー

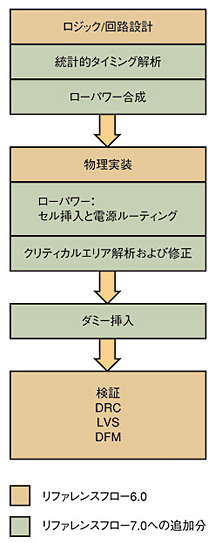

TSMC社は毎年新しいリファレンスフローを発表している。ユーザーはこのフローを参考にして設計上の課題を把握し、特定のノードでどのようなツールを使ったらよいかを知ることができる。2006年7月に米国サンフランシスコで開催されたDesign Automation Conference(DAC)で、TSMC社はリファレンスフロー7.0を発表した(図1)。これにより、顧客はCadence社、Synopsys社、そして2006年新たに加わったMagma社のフローを使ってTSMC社の65nmプロセス向けICを設計できる。これまでと同様、このリファレンスフローにはDFMツールと電力管理のツールが含まれている。しかしTSMC社は2006年、DFMのサブカテゴリとするには議論の余地があるSSTAツールの導入を推奨している。

Wan氏によれば、TSMC社は数年前から、自社の65nmプロセスをサポートするよう大手ツールベンダーに働きかけているという。Cadence、Synopsys、Magmaの3社にはすでに完成されたDFMフローがある。このため、ユーザーがいずれかのベンダーのフローに一本化したいと思うようであれば、TSMC社は「3社のフローがTSMC社の65nmプロセスに適合していることを検証する」と同氏はいう。Synopsys社とMagma社はすでにTSMC社が推奨するSSTA技術を採用している。一方、Cadence社はまだ同技術に対応していない。Cadence社は最近までCMPシミュレーション技術にも対応していなかったが、CMPシミュレーションツールを開発する米Praesagus社を買収することでその体制を整えた。

リファレンスフローに加え、TSMC社はDFM認定プログラムも発表した。サードパーティのDFMベンダーも準拠ツールを提供できるようにするためだ。リソグラフィプロセスの特徴付けとシミュレーションでは、TSMC社はAnchor Semiconductor社の「NanoScope DFP」、Cadence社の「Virtuoso RV」、Clear Shape社の「InShape」、Magma社の「Blast Yield TX」、Mentor社の「Calibre LFD(lithography friendly design)」、Synopsys社の「DFM LCC(lithography compliance checking)」を認定している。CMPシミュレーションでは、Cadence/Praesagus社の「DVIP」、Magma社のBlast Yield TX、Synopsys社の「DFM-CMP」を認定している。CAAでは、Cadence社の「Encounter-CAA」、Magma社のBlast Yield TX、Mentor社の「Calibre YieldAnalyzer」、Ponte社の「Yield Analyzer」、Predictions Software社の「Eyes」、そしてSynopsys社の「IC Compiler」を認定している。今後数カ月のうちにTSMC社が認定するベンダーはさらに増えるだろう。

「多くのユーザーはいろんなツールフローを使いたいだろうし、自作したい人がいることは、TSMC社もよく分かっている」とWan氏はいう。そうしたユーザーに対しては、TSMC社はスクリプトとアプリケーションノート、テストケースを組み合わせたリファレンスキットを提供している。一方でTSMC社は、電力効率と歩留りを同時に向上させるツールとしてBlaze DFM社のツールを推奨している。

柔軟なUMC社のフロー

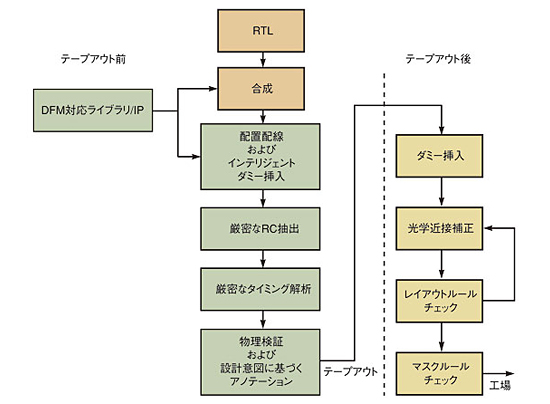

UMC社は、とりわけ配置/配線技術を向上させる一部のDFMツールは同社の65nmフローに欠かせないが、ほかのDFMツールはまだサインオフする必要がないと考えている。「DFMと一口にいっても、そのレベルは多岐にわたり、顧客のニーズも違う」とLin氏はいう。「DFMツールを必要としている顧客もあるが、そうした顧客はサインオフのためにDFMツールを使っているのではなく、将来のプロセスの学習ツールとして使おうとしている。顧客はツールをうまく利用することで65nmでの設計品質を向上させることができる」と同氏はいう。UMC社はどのEDAベンダーの顧客にも応えるというが、同社のDFMフローは図2のようなものとなっている。「当社のリファレンスフローでは、顧客に留意してほしい機能を一応推奨しているが、EDAベンダーが次々に製品を提供してくる限りは、最終的には顧客の選択に任せるしかない。ツールの中には製造プロセスと密に連携しなくてはならないものもある。そのようなツールには高い精度が要求されるため、当社はベンダー数社と協力してその目標の達成に取り組んでいる」とLin氏はいう。

「メタル挿入、ダブルビア挿入、配線拡張など、配線に関連するDFM機能が重要である」とLin氏はいう。この分野では、UMC社はCadence、Synopsys、Magmaの3社と提携している。「配線にかかわることすべてが重要であり、配線のことを話そうと思えば、リソグラフィ、CAA、そして一般的なDFMルールを知っておく必要がある。CAAの重要性は日増しに高くなってきている。ファウンドリが相対的な歩留りデータを提供すべき分野はここだ。これらのツールにより、顧客はコストの観点からトレードオフを推測することができる。顧客からは何らかのデータを提供してほしいとよくプレッシャをかけられる」とLin氏は語る。また、リソグラフィの性能を向上させる2種類のDFM技術の重要性が高まっていると同氏はいう。その1つは、物理設計段階においてリソグラフィの潜在的ホットスポットを特定できるツールである。もう1つは、リソグラフィが形状に与える影響を特定するツールだ。「形状の変化が電気特性に及ぼす影響を測定するためのツールが必要となる。それができるまでにはまだしばらくかかるだろう。設計者はそうしたツールを待ち望んでいるだろうが、統一されたシステムがまだ存在しない」とLin氏はいう。同氏によれば、UMC社はMentor、Clear Shape、Anchor Semiconductorの3社とこの問題に取り組んでいるという。

CMPシミュレーションも重要になってきている。「CMPは厄介な分野だ。大規模な設計では平坦度の問題がよくいわれる。そこでCMPシミュレーションが必要となる。プロセスの初期段階では平坦度が良くなくても、プロセスが進むに連れて良くなってくる」とLin氏はいう。同氏は、配線の層間容量と直列抵抗を正しく反映させるには、抽出ツールのCMPモデルが役に立つという。この分野では、UMC社はCadence社が最近買収したPraesagus社と、より密接に協力し合っているが、Synopsys社とMagma社もこの技術を提供している。

もう1つ期待される分野がSSTAだ。「サインオフのためにSSTAを使う人はまだいない。第1段階はSSTAがチップ上のマージンを小さくできるようにするために使用されると思う。将来は標準的なサインオフツールとして使われるようになるだろう」と同氏はいう。SSTAの分野では、UMC社は新興企業の米Extreme DA社と提携している。また、電力効率と歩留りに影響を及ぼす熱解析では米Apache Design Solution社と提携している。Lin氏はさらに、「リソグラファにとって使いやすく、製造により適合したIP(知的財産)とIPツールも必要だ」とコメントしている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

図1 TSMC社のリファレンスフロー7.0 TSMC社のリファレンスフロー7.0には、DFM、電力管理のツールが含まれている。

図1 TSMC社のリファレンスフロー7.0 TSMC社のリファレンスフロー7.0には、DFM、電力管理のツールが含まれている。 図2 UMC社のDFMフロー UMC社のDFMフローでは、新しいツールに加えてDFMに配慮したIPが強調されている。

図2 UMC社のDFMフロー UMC社のDFMフローでは、新しいツールに加えてDFMに配慮したIPが強調されている。