変化するDFM市場(4/5 ページ)

CISはDFMツールを指定

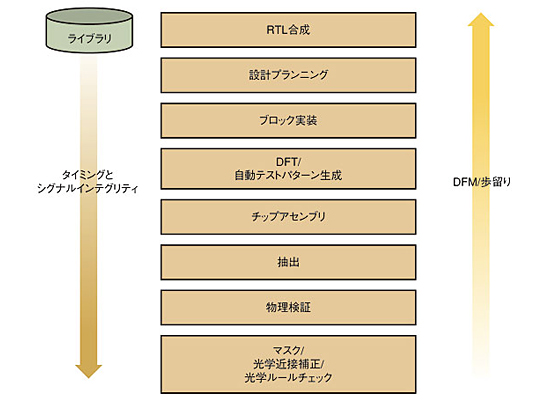

TSMC社とUMC社がフローを確立して、新規参入者との連携を積極的に進めているのに対し、CISアライアンスは顧客のために入念な評価作業を続けている。これにより顧客はツールの評価にかける時間を節約できるだろう。しかし、それはGDSII(graphic design system II)フォーマットのファイルとマスクに必要な調整を施した上で、Chartered社、IBM社、あるいはSamsung社のファウンドリに設計データを送らせることを意図した活動のようにも思える。Chartered社のプラットフォームアライアンス部門シニアディレクタを務めるWalter Ng氏によれば、CISアライアンスが2005年に設立されたときに、3社はDFM設計ガイドラインに焦点を当てた8つの分科会(CAA、リファレンスフロー、リソグラフィベースシミュレーション、形状ベースシミュレーション、タイミングばらつき、DFMサービス、CMPシミュレーション、DFMチェック)を設置したという。そして各分科会でサードパーティのツールを評価し、その結果から1つのフローを導き出した(図3)。「少なくとも評価の時点では最高の技術を選び出した」とNg氏はいう。DFMチェックの分野では、Chartered社はOPCやRET(解像度向上技術)、リソグラフィ関連のツールベンダーとしてMentor社を選定した。

「ルールチェック用のものではあるが、当社はこれを非常に重要なツールだと考えている。ルールからモデルベースのアプローチに完全に移行できるとは考えていない」とNg氏はいう。同社が選んだのはMentor社の「Calibre DFM」(現Calibre YieldAnalyzer)である。「当社では推奨されているルールに重きを置いている。そうすれば顧客はルールに基づいてレイアウトを設計できる」とNg氏はいう。「顧客は最も優先度の高いルールを反映させることで、最も投資効果の高い部分のレイアウトを修正することに集中できる。そして再度そのレイアウトの検証を実行して、そのセルまたはブロックの相対スコアリングが向上したかどうかを確認することができる」。

CAAでは、層ごとの欠陥密度に焦点を当てたPonte Solutions社のモデルベースアプローチをChartered社が選択した。「Ponte社のツールは、評価の時点では最もCAAの精度が高く、ホットスポットを厳密に特定できた」とNg氏はいう。リファレンスフローの分野では、同社はCadence、Synopsys、Magmaの3社と提携している。「3社ともルーティングの性能向上に取り組んでおり、correct by construction(構築しながら修正する)手法をとっている」(Ng氏)。

CMPシミュレーション/挿入ツールはパラメータを正確に抽出し、均一に挿入されるようにタイミング解析とシグナルインテグリティへのフィードバックを行う。CISアライアンスはこのためのツールにCadence/Praesagus社のツールを選定した。

形状/リソグラフィシミュレーションにはMentor社のCalibre LFDが採用された。この共同プロジェクトにより、設計者は製造にかかわる潜在的なトレードオフと影響を特定できるとNg氏は語る。「当社は設計者らとともに、期待通りのことが行える製品かどうかを検証してきた。Calibre LFDの精度が高い理由は、その入力が実際のOPCデッキだからだ」。CISアライアンスはさらに、形状/リソグラフィシミュレーションの分野でClear Shape社とも提携している。同社のツールは抽象化モデルに対応しているためCalibre LFDよりも能力とパフォーマンスに優れているが、CISアライアンスはMentor社のツールの精度がより高いと考えている。「Calibre LFDの精度の高さは魅力だし、Mentor社は常に精度、パフォーマンス、能力の向上にも取り組んでいる」とNg氏は語る。

DFMレイアウトガイドラインに対応したツールは存在しないが、共通プラットフォームを確立しているCISアライアンスは、この分野では競合よりも有利な立場にあると考えている。「CISアライアンスでは量産に堪えうるレベルの推奨レイアウトを数多く用意している」とNg氏は語る。同氏によれば、推奨レイアウトについては度重なる議論が交わされている。「Chartered社、IBM社、Samsung社の間で、複雑さが異なるさまざまな設計が出てくることは仕方がない。当社はクライアント向けのDFMレイアウトガイドラインを協力して作成し、最新の情報や教訓が反映されるように4半期ごとに数回は改訂している」とNg氏はいう。

CISアライアンスは2005年のDAC以来、リーク電流の低減と歩留りの最適化でBlaze DFM社と提携している。「主な顧客とBlaze DFM社のツールを検証し、いくつかのICチップで試してみたところ、非常に期待できる技術であることが分かった」とNg氏はいう。

CISアライアンスは、SSTAの分野で提携している企業の名前を発表していない。しかし、SSTAの研究で長年の実績を誇るIBM社の技術を採用する可能性が高い。IBM社のSSTAツール開発グループは、2005年度のEDN Innovator賞を受賞し、同年SSTAツールを発表した。しかし、まだ市販されていないようだ。「この分野にはかなりの労力と時間を費やしているが、まだ特定の技術を発表していないのは、どんなプロセスにも共通に使えるものがないからだ」とNg氏は語る。SSTA関連の技術のいくつかは将来的には必須となるかもしれないが、今のところはトレードオフの材料にすぎない。「設計者は、何に対してならトレードオフしたいのかをよく分かっている。例えば、歩留りがトレードオフ材料の1つだろう。顧客は『EDAベンダーに望むことは、それらのトレードオフが何であるかを知ってほしい。そうすれば私はそれらのトレードオフを受け入れ、ツールが機能するようにデータを作成しよう』という。これらのツールはいつか危機的局面を迎えるかもしれない。例えば、これらの技術のいくつかは、DRC(design rule check)の論証で終わってしまうことが予想される。状況は複雑になる一方で、45nmの設計ルールは制限的だ」。同氏は、「ルールファイルを組み込むためには大規模なDRCデッキが必要になる」と説明する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

図3 CISアライアンスが選定したDFMフロー

図3 CISアライアンスが選定したDFMフロー