IBISシミュレーションの効果:Baker's Best

高速デジタルシステムの設計者が苦労する問題として、オーバーシュート、アンダーシュート、インピーダンス不整合に起因するリンギング、ジッター、クロストークなどが挙げられる。プリント基板の設計に依存するこうした問題点への対策は、大きな困難を伴う。高速デジタルシステムのシグナルインテグリティ(信号品質)に関するこのような性能評価や対策においては、IBIS(Input/Output Buffer Information Specification)モデルがよく利用される。

IBISモデルは、1990年代初期に登場し、ANSI/EIA 656-Bとして標準化された。2008年8月には同規格のバージョン5がIBIS Open Forumからリリースされている。IBISモデルでは、デバイスのI/O端子からの出力を、I‐V(電流対電圧)特性とV‐t(電圧対時間)特性を規定するテーブル(表)を用いて記述する。このテーブルは、各I/Oセルに対するシミュレーションや計測の結果を基に、デバイス製造メーカーが作成する。

IBISモデルを用いるシミュレーションツールは、転送レートが20ギガビット/秒にも達する高速システムの設計に不可欠なものとなっている。IBISモデルを使った場合、シミュレーションの所要時間がSPICEを使う場合と比べて格段に短くなる。しかも、SPICEを用いる場合と同等に正確な結果が得られる。SPICEはトランジスタレベルから事象を扱うので、対象とするプリント基板の規模が大きくなると、シミュレーションの実行に数日間から数週間を要することになる。それに対し、IBISシミュレーションならば、同じことを数分から数時間で実行できる。IBISシミュレーションで得られる結果としては、伝送ラインの応答特性やアイパターンなどがある。

ユーザーの中には、クロック周波数が40MHz以下といったさほど動作速度の速くないデバイスに対するIBISシミュレーションのサポートを望むものもいる。このような低い周波数の領域においても、デジタル信号の立ち上がり/降下エッジが高速になると、シグナルインテグリティの問題が起きることがあるからだ。例えば、クロックに大きなリンギングが生じると、同じ機器内で使用しているA-Dコンバータに誤動作やゲイン誤差が発生するといったことが起こり得る。

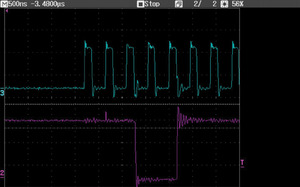

図1に、IBISモデルを使用したシミュレーション結果の例を示した。これは、伝送ラインのインピーダンスについて十分に注意することなく設計された回路のシミュレーション結果だ。図の波形は、回路中のA-Dコンバータの入力部におけるものである。この回路では、A-Dコンバータとプロセッサがそれぞれ別のプリント基板に実装される。2つの基板を接続するのは、長さが1mの単純なカテゴリ5のツイストペアケーブルだ。プロセッサからのクロック(上の波形)の周波数は2.25MHzである。このクロックに同期して、A-Dコンバータからプロセッサにデータ(下の波形)が送信される。

当初、この回路の設計者は、これら2つのデバイスのクロック周波数が低いことから、終端条件が問題になることはないと考えていた。しかし、シミュレーション結果から、この回路の終端条件では、ハイ/ローの閾(しきい)値を超えるほどのリンギング(アイパターンの劣化原因)が発生することが見て取れる。

<筆者紹介>

Bonnie Baker

Bonnie Baker氏は「A Baker's Dozen: Real Analog Solutions for Digital Designers」の著書などがある。Baker氏へのご意見は、次のメールアドレスまで。

bonnie@ti.com

脚注

※1…Green, Lynne, "Understanding the importance of signal integrity," IEEE Circuits and Devices, November, 1999

※2…Wang, Lance, "Case Study: Analyze different results from IBIS simulators," IO Methodology, July 28, 2009

※3…"Using IBIS models for timing analysis," Texas Instruments (SPRA839A), April 15, 2003

Copyright © ITmedia, Inc. All Rights Reserved.