ルネサス、ソフトエラーフリーのSRAMで110nmプロセス品を製品化:ルネサス Advanced Low Power SRAM

ルネサス エレクトロニクスは2013年9月24日、ソフトエラー耐性が高いなどの特徴を持つSRAM製品シリーズとして、回路線幅110nmの製造プロセスを採用した容量4Mビット品を製品化したと発表した。

ルネサス エレクトロニクス(以下、ルネサス)は2013年9月24日、ソフトエラー耐性が高いなどの特徴を持つSRAM製品シリーズとして、回路線幅110nmの製造プロセスを採用した容量4Mビット品を製品化したと発表した。2013年11月からサンプル出荷を開始する。従来の150nmプロセス採用品と同等のソフトエラー率を達成しているという。

今回発表したのは、ルネサスの主力SRAM製品「Advanced Low Power SRAMシリーズ」の最新製品。同シリーズは、シリコン基板に外部からアルファ線や中性子線が入射した際に、基板中で発生した電荷によりメモリの情報が失われる現象であるソフトエラーやラッチアップ*)に対する耐性が高いという特徴を持つ。メモリセルの記憶ノードにキャパシタを付加することで、ソフトエラーに対する高い耐性を実現している。

*)CMOSトランジスタのウェル、Si基板、P型拡散層、N型拡散層により形成されるNPN、PNP構造(寄生バイポーラトランジスタ)が、電源や入力端子からの過電圧によりオン状態となり、電源と接地の間に大電流が流れる現象。

「実質ソフトエラーフリー」

一般的にソフトエラー対策としては、発生したソフトエラーをSRAMやユーザーシステム内部に組み込んだECC(Error Correcting Code)回路で訂正する方法があるが、ECCの性能によっては複数ビットのエラーを訂正できないなど、エラー訂正に限界が生じる。一方、Advanced LP SRAMではソフトエラーの発生そのものを抑制する構造的対策を講じ、既に量産している150nmプロセス採用品でも「システムソフトエラー評価結果から、実質ソフトエラーフリーといえる耐性を確認している」(ルネサス)とする。

同時に、SRAMセルのロードトランジスタ(Pチャネル)をポリシリコンTFTで形成し、シリコン基板上に形成されたNチャネルMOSトランジスタの上層に積層されるため、下地のシリコン基板上にはNチャネルトランジスタのみで形成されている。これによりメモリ領域内では寄生サイリスタ構造は存在せず、原理的にラッチアップが発生しない構造となっているという。

これらの特徴から、同シリーズは、FA機器、計測器、スマートグリッド関連機器や交通システムなどの高い信頼性が要求される用途で使用されている。

セルサイズは「65nmプロセスのフルCMOSタイプに匹敵」

2013年11月からサンプル出荷する110nmプロセス採用品でも、従来品と同等の特徴を備え、ソフトエラー率は「150nmプロセス品と同等」(ルネサス)という。また同シリーズは、SRAMのポリシリコンTFT積層技術とスタックトキャパシタ技術の融合により、セルサイズの小型化を実現し、「例えば、110nm Advanced LP SRAMのセルサイズは65nmプロセスによるフルCMOSタイプに匹敵する」としている。

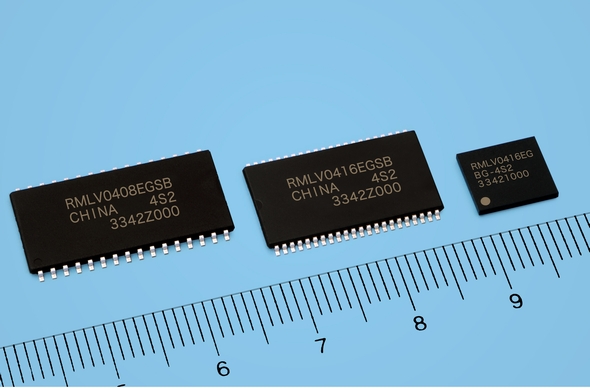

新製品は、パッケージなどが異なる「RMLV0416Eシリーズ」「RMLV0414Eシリーズ」「RMLV0408Eシリーズ」の3シリーズ12品種があり、サンプル価格はいずれも630円となっている。

ルネサスでは、今後110nmプロセス品として、8M〜64Mビットまでの各容量の製品を投入していく予定だ。

関連記事

ルネサスとADIが両社の評価ボードを接続する基板を共同開発、「評価環境設定時間を7割短縮」

ルネサスとADIが両社の評価ボードを接続する基板を共同開発、「評価環境設定時間を7割短縮」

ルネサス エレクトロニクスとアナログ・デバイセズの日本法人は、両社の評価ボードを接続するインターポーザボード「SE SPIDER-01」を共同開発したと発表した。「評価環境を設定する時間を約7割短縮できる上、ノイズの発生を抑制できるため、安定した評価値を得られる」(両社)としている。 スマホで「一眼カメラ並み」の光学式手振れ補正を実現するIC

スマホで「一眼カメラ並み」の光学式手振れ補正を実現するIC

ルネサス エレクトロニクスは、スマートフォンやタブレット端末向けた光学式手振れ補正用ドライバICを発表した。「スマートフォンやタブレットPCのカメラ機能をデジタルスチルカメラ並みに高性能化できる」(同社)。 ルネサス 中学必修の「プログラム制御」を学べる“マイコンカー”を発売

ルネサス 中学必修の「プログラム制御」を学べる“マイコンカー”を発売

ルネサス エレクトロニクスなどは、小学校高学年/中学生でも簡単にマイコンのプログラミングを体験できるロボットカーを開発し、2013年7月末から販売を始める。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

110nmプロセスを採用した「Advanced Low Power SRAMシリーズ」

110nmプロセスを採用した「Advanced Low Power SRAMシリーズ」