周期波形を矩形波に変換する回路:Design Ideas 信号源とパルス処理

データからクロック信号を抽出する時などに欠かせない「周期波形を矩形波に変換する回路」として、変換回路にデューティー比を制御できる機能が備わった回路を紹介する。

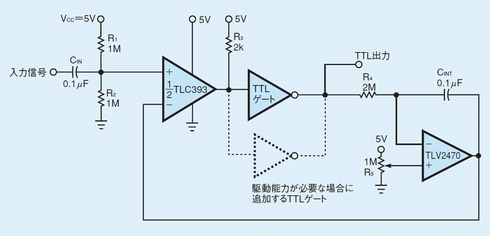

ある周期波形を矩形波に変換する回路は、データからクロック信号を抽出したり、波形発生器を作成したり、タイミング・パルス発生器を作ったりする際に欠かせない。この変換回路にデューティー比を制御できる機能が備わっていれば、なお有用である。図1に示す回路は、このような特性を有し、さらに複数のTTL互換負荷を駆動できる。

まずR1とR2を使って直流電圧のレベルを決める。R1=R2に設定すれば、このレベルはVCC/2になる。CINを使うことで、入力信号とこの直流電圧レベルを結合させる。この結果、コンパレーターの非反転入力に加わる周期信号がVCC/2以上になったり、それ以下になったりするわけだ。

入力から見たときに並列接続となる抵抗R1とR2の合成値(RP)とCINによって、−3dBのカットオフ周波数が1/(2πRPCIN)になる高域通過フィルターを形成する。この回路を低周波用途に使う場合は、カットオフ周波数を下げるためにRP、もしくはCINの値を増やせばよい。入力信号に重畳された高周波雑音が問題となる場合は、抵抗R2と並列にコンデンサーを接続する。このコンデンサーを追加することで高周波雑音を除去できる。さらに入力信号が矩形波であれば、立ち上がり時間と降下時間は長くなる。こうすれば、回路の制御範囲を広げられる。

入力信号が対称波形である場合、直流電圧レベルをVCC/2に設定すれば、パルス幅とデューティー比の制御範囲が最大になる。しかし入力信号が非対称の場合は、設定する直流電圧レベルを変えなければならない。仮にVCC/2に設定してしまうと、VCC/2を超える正の時間と、それを下回る負の時間が等しくならないからだ。このためRPの値は、こうして発生したオフセット電圧によって入力バイアス電流が流れないように十分に小さくしなければならない。

コンパレーターには、業界標準になっている「LM393」のCMOS版である「TLC393」を使った。このコンパレーターは、積分器から出力された基準電圧と、R1とR2で決まる直流レベルにシフトした入力信号を比較する。比較の結果として出力される信号の波形は、矩形波になる。コンパレーターは、R3を介して1つのゲートを駆動する。なお、高い駆動能力が必要な場合は、複数のゲートを用意する。ここでR3は、ローレベルからハイレベルに遷移する間にゲート入力を素早く充電するために低い値にしなければならない。コンパレーターが引き込める電流はR3の値で制限されてしまう。

「TLV2470」は積分器である。コンパレーターが出力した矩形波を積分/反転させて、コンパレーターの基準電圧としてフィードバックする。積分器の非反転入力がVCC/2であれば、出力される矩形波は対称波形になり、その平均値はVCC/2となる。可変抵抗R5をその中心値に設定すると、デューティー比が50%の矩形波が得られる。R5を接地レベルに近づけると、ほとんどの期間がローレベルの矩形波が得られる。一方、VCCに近づけると、ほとんどの期間がハイレベルの矩形波になる。

積分器の極は、fP=1/(2πR4CINT)となる。図1に示した回路素子の値の場合、0dBを横切る周波数(クロスオーバー周波数)は0.8Hz。積分器の利得は0.8Hzで1となり、20dB/ディケード(周波数で1桁当たり)で減少する。従って、コンパレーターの小信号利得は、発振を引き起こすほど大きな値ではない。積分器の極の選択は、安定性と制御応答時間のトレード・オフになる。図1の回路は、2〜98%の範囲で矩形波のデューティー比を制御できる。20mVの入力信号から動作する。

Design Ideas〜回路設計アイデア集

【アナログ機能回路】:フィルタ回路や発振回路、センサー回路など

【パワー関連と電源】:ノイズの低減手法、保護回路など

【ディスプレイとドライバ】:LEDの制御、活用法など

【計測とテスト】:簡易テスターの設計例、旧式の計測装置の有効な活用法など

【信号源とパルス処理】:その他のユニークな回路

※本記事は、2008年7月29日にEDN Japan臨時増刊として発刊した「珠玉の電気回路200選」に掲載されたものです。著者の所属や社名、部品の品番などは掲載当時の情報ですので、あらかじめご了承ください。

「珠玉の電気回路200選」:EDN Japanの回路アイデア寄稿コラム「Design Ideas」を1冊にまとめたもの。2001〜2008年に掲載された記事の中から200本を厳選し、5つのカテゴリに分けて収録した。

関連記事

- Design Ideas 信号源とパルス処理

PSoCで構成するディレイパターン生成器

PSoCで構成するディレイパターン生成器

デジタル回路、アナログ回路を問わず、実験などの目的でディレイパターンが必要となるケースは多い。このような状況に対応可能なものとして、筆者は1個のICでディレイパターン生成器を構成する方法を考案した。 電源コントローラICをパルス発生器として使う

電源コントローラICをパルス発生器として使う

スイッチングレギュレータ用コントローラICをパルス発生器として利用する方法を紹介する。立ち上がり/降下時間が2ns未満のゲート駆動用パルスを発生させることができるようになる。 パルス幅を電圧に変換する回路

パルス幅を電圧に変換する回路

今回は、パルス幅を電圧に変換する回路を紹介する。1つのパルス信号の入力が終わるまでの期間を直流電圧に変換する回路である。 オペアンプを使ってVCAを線形化

オペアンプを使ってVCAを線形化

オペアンプを用いてVCA(電圧制御アンプ)の利得を線形化するアイデアを紹介する。

Copyright © ITmedia, Inc. All Rights Reserved.