FETプローブでRFスペアナの測定範囲を拡大:Design Ideas 計測とテスト(2/2 ページ)

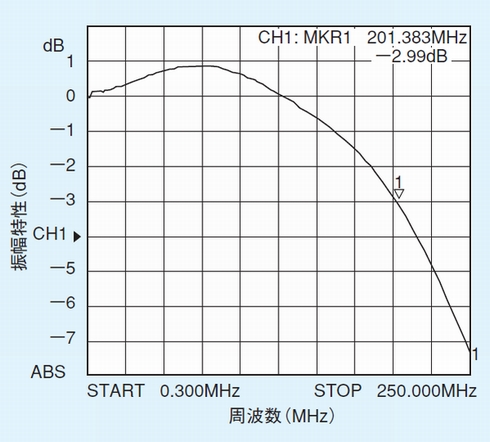

IC1は、Texas InstrumentsのFET入力オペアンプ「OPA656」で、電圧利得2を提供する。この回路構成では帯域幅が約200MHzになる(図2)。OPA656は、100Ωのトータル負荷に対して50Ωのバック整合負荷を駆動しているので、6dBの損失となり、IC1の利得2(6dB)と相殺して、正味で利得1になる。OPA656が発生するノイズと歪は、市販のFETベースのアクティブプローブの大部分に比べて少ない。

図2:プローブの周波数特性 (クリックで拡大)

図2:プローブの周波数特性 (クリックで拡大)このプローブの−3dB周波数特性は、10Hz〜200MHzと広く、通過域リップルは1dBより若干小さく、市販のアクティブFETプローブの多くの±2dBに比べて優れている。

他のコネクターに容易に合わせることが可能

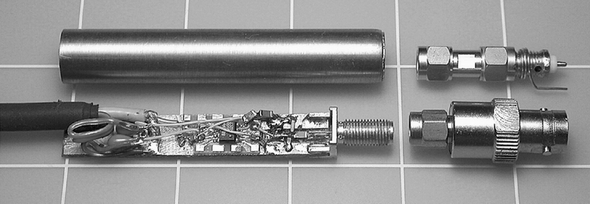

プローブは図3のように、真ちゅうのチューブに収まる。入力コネクターは小型のSMA型(ネジかん合型)で、BNC型(バイオネットロック型)など他のコネクターに容易に合わせられる。必要な電源は5Vや−5Vで約18mA。測定器側のプローブ電源コネクターか、ACアダプターを用いたリニア電源から取ればよい。最良の結果を出すには、「78L05」および「79L05」ボルテージレギュレーターを用いて電源電圧を安定化する。

図3:プローブの外観 (クリックで拡大)

図3:プローブの外観 (クリックで拡大)1枚の基板上に組み立てて、ホビー用の真ちゅう管に収めることができる。SMA入力コネクターは、多数のアダプターやプローブに合う。プローブの出力端は、ゴム製グロメット(歯付座金)で閉じる。

標準の50Ω細芯同軸ケーブルを用いてプローブを測定器に接続する。周波数特性を平たんにし、均一な利得を得るには、プローブの出力を50Ωで終端する。その際、DC出力ブロッキング用コンデンサーは不要である。

Design Ideas〜回路設計アイデア集

【アナログ機能回路】:フィルタ回路や発振回路、センサー回路など

【パワー関連と電源】:ノイズの低減手法、保護回路など

【ディスプレイとドライバ】:LEDの制御、活用法など

【計測とテスト】:簡易テスターの設計例、旧式の計測装置の有効な活用法など

【信号源とパルス処理】:その他のユニークな回路

※本記事は、2008年7月29日にEDN Japan臨時増刊として発刊した「珠玉の電気回路200選」に掲載されたものです。著者の所属や社名、部品の品番などは掲載当時の情報ですので、あらかじめご了承ください。

「珠玉の電気回路200選」:EDN Japanの回路アイデア寄稿コラム「Design Ideas」を1冊にまとめたもの。2001〜2008年に掲載された記事の中から200本を厳選し、5つのカテゴリに分けて収録した。

関連記事

LEDを光センサーとして使い、照明強度を計測

LEDを光センサーとして使い、照明強度を計測

LEDは表示用や照明用といった一般的な用途だけでなく、光起電力型の検知器(光センサー)としても使用可能である。今回は、LEDを光センサーとして使用する回路図を紹介する。 小電流電源の試験に適した定電流負荷

小電流電源の試験に適した定電流負荷

市販の電子負荷機器の多くは、電流値が少ないスイッチ電源の試験において精度面で問題が生じる場合がある。今回は、この問題に対する解決策の一案として、定電流負荷回路を紹介する。 安価な「電圧降下法」で基板の短絡を検出する

安価な「電圧降下法」で基板の短絡を検出する

プリント基板の製造で、圧倒的に多い不良は配線パターン間の短絡だ。短絡箇所を探すのには非常に多くの時間を要し、その作業にはストレスが伴う。そこで、今回は4線式DMMや抵抗測定器の考え方を用いた、短絡箇所を発見する簡単な方法を紹介しよう。 白色LEDドライバに調光機能を付加する

白色LEDドライバに調光機能を付加する

カラー表示を備える携帯電話では、消費電力の要求が厳しい。新しいアプリケーションが次々と登場し、低電力設計が不可欠になっている。そこで、今回提案したいのは応用範囲の広い調光方法だ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- 「解読不可能」を破る量子コンピュータ――今から始める暗号セキュリティ

- Intelが「Core Series 3」モバイルプロセッサ、エッジ機器向けに

- フェライト(3) ―― 電子部品としてのフェライト

- アルミ電解コンデンサー(1)―― 原理と構造

- AI/HPC用ガラスビア向け 低収縮特性の銅ナノペースト

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- 次世代車載向けセキュリティコントローラー