オペアンプのダイナミック応答の検討(2) タイプ2補償回路の伝達関数:アナログ回路設計(6/8 ページ)

【付録】インピーダンスの計算

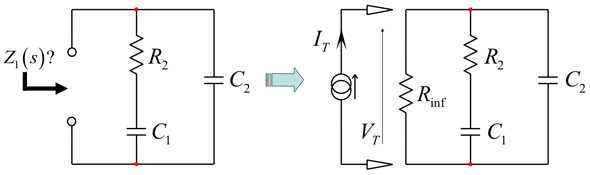

7式で与えられるインピーダンスを計算するには、参考資料4で詳述されている高速分析手法を適用できます。回路図を図18に示します。インピーダンスを求めるには、電流源ITを使用して回路網に電流を流します。ITは「刺激」でありVTは「応答」です。求めようとしている伝達関数は刺激と応答を結びつける関係式です。分析を容易にするために、測定端子間にダミー抵抗Rinfを接続しました。この抵抗を使用する理由は後述します。

このような回路網の伝達関数は、次の形式で表すことができます。

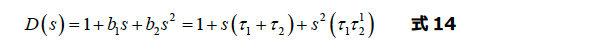

2次システムの場合、分母が次の式に従うことを示すことができます。

τ1とτ2は、全てのエネルギー蓄積素子(つまりCとLs)がそれぞれのDC状態(コンデンサーは開路、インダクターは短絡)になったままの時に得られる時定数です。τ21は、時定数2の要素の端子間に見られる抵抗を求める際に時定数1(上付きの数字)に含まれる要素が高周波状態(コンデンサーは短絡、インダクターは開路)に置かれていることを意味します。逆にτ12は、時定数1の要素の端子間で見られる抵抗を求める際に、時定数2(上付きの数字)の要素が高周波状態(コンデンサーは短絡、インダクターは開路)に置かれていることを意味します。次に、これらの時定数を組み合わせて式14に示すようにD(s)を形成します。

最初に、s=0の時にエネルギー蓄積素子の端子間で見られる抵抗に注目します。DC状態では、全てのコンデンサーを開路とみなしインダクターを短絡とみなします(これらが存在する場合)。SPICEは、.TRANまたは.ACいずれのタイプの分析でも、分析開始前にバイアスポイントを決定する際に同じ作業を実行します。頭の中で、全てのコンデンサーを取り外した場合に、入力端子間の抵抗をRinf,として固定します。したがって、この抵抗により無限項を回避できます。

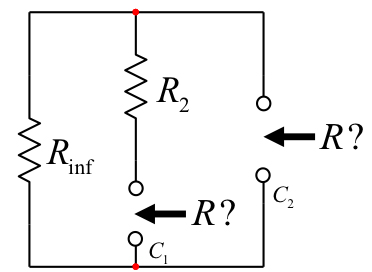

次に、各コンデンサーの端子間の抵抗Rを決定します。このステップに対応するのはDC状態のままに(コンデンサーを開路にするか取り外す)しておくことです。図19に簡単な図を示します。時定数はτ=RCで得られます。

代数式を1行も記述することなく、この図を検討してコンデンサーの端子間から見た抵抗値を「確認」することができます。次の式が得られます。

および、

Copyright © ITmedia, Inc. All Rights Reserved.

図19:ここで、各コンデンサーがDC状態にある(回路から取り外されている)場合を想定して、各コンデンサーの両端子の抵抗を求めることができる

図19:ここで、各コンデンサーがDC状態にある(回路から取り外されている)場合を想定して、各コンデンサーの両端子の抵抗を求めることができる