アクティブクランプ・フライバックで超高密度「USB PD 3.0」設計に対応:GaNも使える

100Wのプログラマブル電源(PPS)向けUSB PD(Power Delivery) 3.0などの新しい用途や急成長するアプリケーションが、しばしば超高密度(UHD)であると言及される、より小型でコンパクトなスイッチング電源(SMPS)フォームファクタの需要を促進しています。

超高密度(UHD)市場の動向とトレードオフ

100Wのプログラマブル電源(PPS)向けUSB PD(Power Delivery) 3.0などの新しい用途や急成長するアプリケーションが、しばしば超高密度(UHD)であると言及される、より小型でコンパクトなスイッチング電源(SMPS)フォームファクタの需要を促進しています。

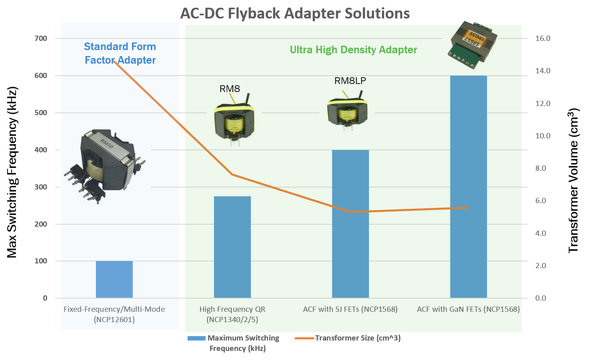

図1に示すように、スイッチング周波数を高くするとトランスの容量が減少し、UHDのメリットが得られます。しかし、スイッチング周波数を高くすると電力損失が増加するため、フライバック・アーキテクチャを進化させる必要が生じます。100kHzまでの固定周波数/マルチモードフライバック・スイッチは、標準的なスイッチング電源アダプターに搭載される大型トランスを駆動します。準共振(QR)フライバックに移行すると、スイッチング周波数が280kHzまで増加するため、トランスを小型のRM8フォームファクタに縮小できます。アクティブ・クランプ・フライバック(ACF)を採用すると、スイッチング周波数が最大450kHzになるため、より低プロファイルのRM8LPトランスを使用できるようになります。最後に、シリコン接合型(SJ)FETを窒化ガリウム(GaN)FETに置き換えると、600kHz以上のスイッチング周波数が可能となり、トランスをさらに小型にできます。

フライバックトポロジー

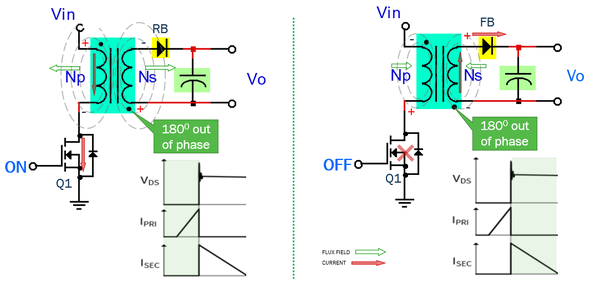

フライバックは、主に低コストで使いやすいという理由から、低・中電力のAC-DCコンバーターによく採用されるトポロジーです。フライバックはDC入力を前提としており、2次側のトランス、電源スイッチ(Q1)、ダイオードが含まれます(図2)。トランス(図中の点線は1次側と2次側で180度位相がずれていることを示す)は結合インダクターであり、電源スイッチがオフのときにのみ、1次側から2次側にエネルギーが転送されます。

フライバック動作

電源スイッチ(Q1)がオンになると(図3の左)、VINから電流が流れ、1次側と2次側の両方のインダクターにエネルギーが蓄積されます(磁界が拡大)。180度の位相反転によりダイオードが逆バイアスされるため、2次側には電流が流れません。

電源スイッチがオフになると(図3の右)、1次側と2次側の磁束が崩れ始め、1次側の極性が変化し(フライバック動作)、ダイオードに順方向バイアスがかかるため2次側に電流が流れるようになります。

フライバックの漏れインダクタンス

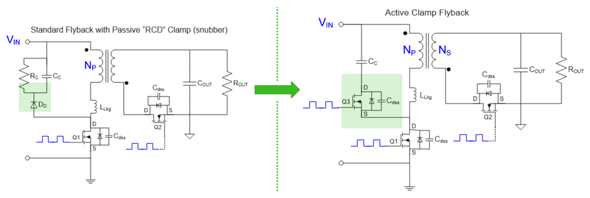

残念ながら、電源スイッチ(Q1)がオフになると、1次側の漏れインダクタンス(LLkg)が電源スイッチ、ドレイン-ソース間容量(Cdss)と相互作用して、VDSで過剰なリンギングを引き起こし、MOSFETに損傷を与える可能性があります(図4の左)。そこで、RCD(抵抗/コンデンサー/ダイオード)スナバ回路(RCDクランプ)を追加するとMOSFETを保護できるようになります(図4の右)。スナバ回路は漏れインダクタンスのエネルギーをMOSFETのドレインからスナバのキャパシター(CC)を移動させ、抵抗(RC)で熱として放出します。ただし、スナバによってフライバックの全体的な効率が向上するわけではありません。

2次側の同期整流(SR)

フリーホイーリングダイオード(還流ダイオード、図5の左)をMOSFET(図5の右、Q2)に置き換えると、2次側の効率が向上します。MOSFETのオン抵抗(RDSON)の電力損失は、シリコンダイオード(0.6V順方向バイアス)や、場合によってはショットキーダイオード(0.3V)よりもはるかに少なくなります。

バレースイッチングと疑似共振フライバック

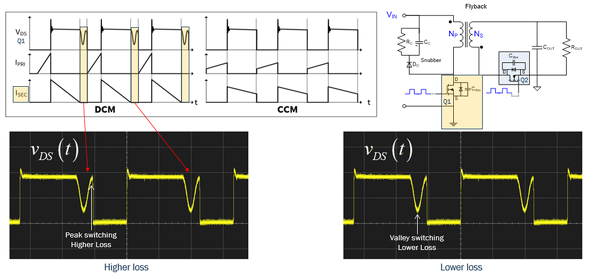

2次側電流(ISEC)がゼロまたは不連続モード(DCM)に達した後に、電源スイッチQ1のVDSは、インダクタンスや寄生容量によって発振を起こすことがあります(図6)。このような発振は“バレー(谷)”を形成します。バレースイッチング(疑似共振スイッチング)は、次の電源スイッチをオンにする最も深い“谷”、つまりVDSが最小となるポイントを探します。簡単に言えば、電力損失は、VDSの波形のピーク時にQ1をオンにすると増加し、谷の時にQ1をオンにすると減少します。

アクティブクランプ・フライバック(ACF)

クランプダイオード(図7の左)をMOSFET(Q3)に置き換えると(図7の右)、効率が向上すると同時に、電源スイッチ(Q1)を保護することが可能です。

アクティブクランプ・フライバック(ACF)アーキテクチャは、漏れインダクタンスを負荷に再循環させることができます。図8の相対タイミング図を参照すると、電源スイッチ(Q1)はT0でオンになり、T2でオフになります。T2で漏れインダクタンス(ICLAMP)がアクティブクランプ(Q3)のボディダイオードに流れ始め、クランプコンデンサー(VCLAMP)が充電されます。T4でQ3がオンになり、クランプコンデンサーの充電が継続されます。T5でICLAMPは負になり、クランプコンデンサーがQ3を通じて、T7まで漏れインダクタンスを負荷に放電します。

T9からT10までの間は、アクティブクランプ(Q3)は、次のQ1オン時間までVDSを0Vに安定化させます。これがZVS(ゼロ電圧スイッチング)です。ZVSではFET容量はゼロです。そのため、ターンオン時のスイッチング損失がゼロになり、高い効率を達成できます。これは一種の「ソフトスイッチング」であり、EMIの点でもメリットがあります。

ACFの欠点

ACFにはいくつかの欠点があります。上述した図8の相対タイミング図を参照すると、T5からT7の間、ICLAMPが下降するにつれて磁束密度が増加し、その結果、上述の図4のRCDスナバの場合と比較して、アクティブクランプ・コアの損失がわずかに大きくなります。もう一つの欠点は、Q1がオフの間にICLAMPがトランスの1次巻線に流れ込むことです。これにより、1次巻線損失が増加します。

onsemiの「NCP1568」は、ACFトポロジーを実装するために設計された、高集積のAC-DC PWMコントローラーです。ZVSが可能で、高効率かつ高周波動作の高電力密度アプリケーションを実現できます。

NCP1568のLDRV出力は、市販されている大部分のスーパージャンクション(SJ) MOSFETを外付け部品なしで直接駆動することができます。SJ MOSFETをGaN(窒化ガリウム) FETに置き換えると、スイッチング周波数をさらに上げることができます。ただし、GaNはSJ MOSFETよりもコストは高くなります。

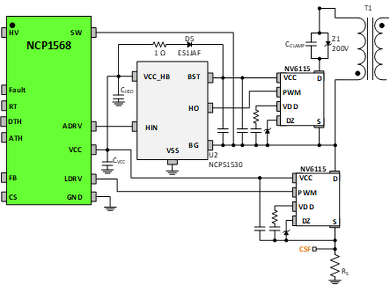

Navitas Semiconductorの「NV6115」は650VのGaNパワーICで、5V/15Vの入力に対応します。図9の構成では、NCP1568からの駆動信号で、システムのニーズを十分に満たすことが示されています。

USB PD 2.0/3.0の比較

USB PDのソースは最大7つのPower Data Objects(PDO)を通知することができ、ソースポートの給電能力をPD対応のシンクに提示するのに使用されます。PDOは、PD 2.0では電圧、電流ともに固定ですが、PD 3.0では3.3Vから21Vまでのプログラマブルな電圧設定範囲(20mVステップ)と、最大5Aのプログラマブルな電流設定範囲(50mAステップ)を備えています(表1)。プログラマブル電源(PPS)の利点は、ソースがより細かな電圧/電流の変化を提供でき、USB Type-Cのソースとシンク間の効率を向上できることです。

onsemiのUSB PDソースコントローラー「FUSB3307」は、USB PD 3.0 v1.2とUSB Type-C r1.4に準拠し、3.3V〜21V(20mVステップ)のVBUSと最大5A(50mAステップ)、合計7つまでの固定およびプログラマブル電源 PDOを供給できます。FUSB3307は、MCUを使用しない低コストのハードウェア・ステートマシン・ソリューションです。ファームウェアの開発が不要なため、多くの機能を搭載した改ざん防止ソリューションを短期間で市場に投入することが可能です。

超高密度(UHD)電源は、100W USB PD 3.0 プログラマブル電源(PPS)を含む多くのアプリケーションで大きな需要があります。アクティブクランプ・フライバックは、コストとUHD性能の間で最適なバランスを実現する「最良のアーキテクチャ」です。その理由は、GaNの追加コストなしで29W/in3の電力密度を達成し、最大92%の4点効率を実現できるからです。また、アプリケーションで一層の効率向上を図るべくさらにコストをかけることが可能な場合、アクティブクランプ・フライバックはGaNパワーデバイスを用いてさらに高い効率と電力密度を達成できます。

【著者:Bob Card/onsemi Advanced Solutions Group(ASG) Marketing Manager】

関連記事

ついにやってきたUSB Power Delivery(USB PD)とは

ついにやってきたUSB Power Delivery(USB PD)とは

USB Power Delivery(USB PD)をご存じでしょうか? 100Wまでの給電を全てUSBケーブルで行ってしまうという新しいUSB規格。既にUSB PDの仕組みを搭載したPCも発売されています。ここでは、あらゆる機器の給電スタイルを一新する可能性のあるUSB PDがどのような規格で、どんなことができるかなどを解説していきます。 USB PDとUSB-Cの充電設計開発キットを発表

USB PDとUSB-Cの充電設計開発キットを発表

ルネサス エレクトロニクスは、USB PDとUSB-Cのバッテリー充電設計に向けたレファレンスデザインキット「RTK-251-1PowerBank3」「RTK-251-BuckBoosterConverter2」を発表した。 USB PD対応昇降圧同期整流DC-DCコンバーター

USB PD対応昇降圧同期整流DC-DCコンバーター

新日本無線は、USB PD規格に対応した、出力電圧切替機能内蔵の昇降圧同期整流DC-DCコンバーター「NJW4210」のサンプル出荷を開始する。居室内および、車室内のUSB PD対応給電システムやUSB PD対応電気機器などでの用途を見込む。 USB Type-C昇降圧バッテリーチャージャーとは

USB Type-C昇降圧バッテリーチャージャーとは

リバーシブルなUSB Type-Cケーブル/コネクターの普及がはじまっている。そして、電源ケーブルもUSB Type-Cによる給電に移行しようとしているが、双方向での給電が可能になるなど根本的な電源供給アーキテクチャの変更が必要になる。そうした中で、登場してきたUSB Type-Cでの給電を可能にする「USB Type-C昇降圧バッテリーチャージャー」とはどのようなものか、紹介していこう。 USB Type-C準拠の垂直レセプタクルコネクター

USB Type-C準拠の垂直レセプタクルコネクター

日本航空電子工業は、USB Type-Cに準拠した「DX07」シリーズに、SMTタイプの垂直レセプタクル「DX07S024WJ4」を追加した。基板の厚さを問わず実装可能で、水平垂直基板が混在する機器での配線自由度が向上する。

Copyright © ITmedia, Inc. All Rights Reserved.