SiC MOSFETを効率よく駆動するゲートドライバーICの選び方:デバイスの特性を生かす(2/2 ページ)

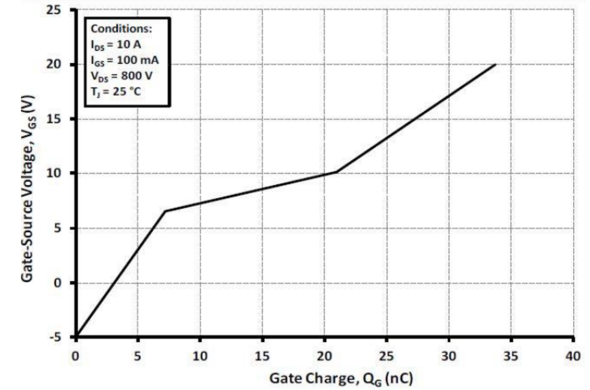

ゲート電荷

SiC MOSFETにゲート電圧(VGS)が印加されると、ゲート電圧ができるだけ早くVGS (MIN) (VEE) からVGS (MAX) (VDD) に上昇するように電荷が転送されます。デバイスの内部容量は非線形なので、VGS対ゲート電荷(QG)曲線を用いて、特定のVGSに対して供給する必要がある電荷量を特定できます。SiC MOSFETのこの「ミラープラトー」は、VGSが高いときに発生し、シリコンMOSFETの場合のように平たんではありません。平たんでないミラープラトーは、対応する電荷QGの範囲でVGSが一定でないことを示しており、これはデバイスのゲインが低いために生じるもう一つの結果です。

また、VGS=0Vでは、QG=0nC(SiC MOSFETをターンオフするのに必要な電荷量が発生しない)なので、ゲートをフルに放電するにはVGSをグランド以下(この場合は−5V)に引き込む必要があることにも注目してください。

SiC MOSFETをターンオンまたはターンオフするのに必要な電荷量を測定したいので、Qgの増加分(あるいは蓄積分/変動分)のみを曲線でプロットしています。この値もQgと呼ばれます。少し混乱しそうです。このグラフは必要なエネルギー量として解釈すべきで、ゲート-ソース間コンデンサーに蓄えられた絶対エネルギーとして解釈しないようにしてください。

負のゲートドライブブロッキング電圧を使用する主な理由は、オフ状態時のドレイン電流リークを低減するためです。これも低いトランスコンダクタンスゲインに起因します。また、負のブロッキング電圧を使用すると、主にターンオフ時のスイッチング損失も減少します。

従って、ほぼ全てのSiC MOSFETで、オフ状態時には−5V<VGS(MIN)<−2Vの範囲の最小VGSを使用することが推奨され、メーカーによってはこの電圧を最小−10Vまで規定しています。

非飽和(DESAT)の保護

DESAT保護は、IGBTをドライブする回路に由来する過電流検出の一種です。オン時間中にIGBTを飽和状態に保持できなくなると(非飽和)、コレクタ-エミッタ間電圧が上昇し、大きなコレクタ電流が流れます。これは明らかに効率に悪影響を及ぼし、最悪の場合、IGBTの故障を引き起こす可能性があります。

いわゆる「DESAT」機能は、IGBTのコレクタ-エミッタ間電圧を監視し、破壊につながる可能性のある状態の発生を検出します。SiC MOSFETの故障メカニズムは多少異なりますが、最大ID(ドレイン電流)が流れている間にVDSが上昇して同様の運命をたどる可能性は否めません。この望ましくない状態は、ターンオン時の最大VGSが低すぎる場合、ゲートドライブのターンオンエッジが遅すぎる場合、または短絡や過負荷状態が存在する場合に発生する可能性があります。最大IDの状態でRDSが増大し、予期せぬVDSの上昇を引き起こすことがあるのです。

SiC MOSFETが非飽和状態になると、VDSは極めて迅速に応答しますが、オン抵抗が増加するため最大ドレイン電流が継続的に流れます。VDSが所定のしきい値に達すると、保護機能を作動させることができます。VDSの検出が遅れるとこの現象を捉えきれない場合があるので、特に注意が必要です。従って、DESATはゲートドライブ回路を保護するための重要かつ補完的な役割を担っています。

ダイナミックスイッチング

SiC MOSFETのターンオンとターンオフのスイッチング状態には、4つの明確なフェーズがあります。図4に示すダイナミックスイッチング波形は、理想的な動作条件を代表するものです。それでも、実際にはリードやボンドワイヤのインダクタンス、寄生容量、PCBレイアウトなどのパッケージの寄生要素が実際の波形に大きな影響を与える可能性があります。スイッチング電源アプリケーションで使用されるSiC MOSFETの性能を最適化するには、適切なコンポーネントの選択、PCBレイアウトのベストプラクティス、適切に設計されたゲートドライブ回路への重点的な取り組みが不可欠です。

SiC MOSFETのゲートドライバーに必要な要素

高効率かつ高速スイッチングを実現しつつデバイスの低ゲインを補うための、SiCゲートドライブ回路に対する重要な要件を、以下にまとめてみます。

- 大部分のSiC MOSFETは、−5V>VGS>20Vの範囲でドライブするときに最高の性能を発揮します。利用可能なデバイスの最大範囲をカバーするには、ゲートドライブ回路はVDD=25VおよびVEE=−10Vに耐えること

- VGSの立ち上がりエッジと立ち下がりエッジは高速(数ナノ秒)であること

- ミラープラトー領域全体で高ピークゲート電流(数アンペア)をソースおよびシンクする能力

- シンク電流能力は、VGSがミラープラトーを下回ったときに、非常に低いインピーダンスのホールドダウンまたは「クランプ」を提供するために必要です。シンク電流定格は、SiC MOSFETの入力容量の放電にのみ必要な値を上回る必要があります。10A程度の最小ピークシンク電流定格で、高性能ハーフブリッジパワートポロジーに対応できなければなりません。

- スイッチング開始前にVGS > 〜16V要件に適合するVDD低電圧ロックアウト(UVLO)レベル

- 負電圧レールが許容範囲内であることを保証するVEE UVLO監視機能

- SiC MOSFETの長期安定動作のための検出、故障報告、保護が可能な非飽和機能

- 高速スイッチングのための低寄生インダクタンス

- SiC MOSFETのできるだけ近くに配置可能な小型ドライバーパッケージ

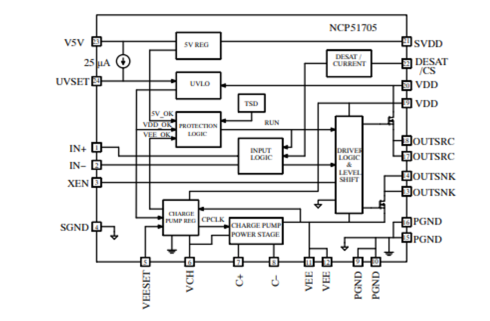

onsemiはこのような要件を満たしたSiCゲートドライバーICの一つとして「NCP51705」を提供しています。

SiC MOSFETはゲインが低いため、適切なゲートドライバーICを選択することが重要になります。汎用のローサイドゲートドライバーには、SiC MOSFETを効率よく確実に駆動するための性能が不足しているので、本稿で解説した要件や要素を考慮して、選択してください。

【筆者:Didier Balocco, Business Marketing Engineer, onsemi】

関連記事

急成長するSiCとGaNパワー半導体、その現状を知る

急成長するSiCとGaNパワー半導体、その現状を知る

急激な成長を遂げるSiC(炭化ケイ素)およびGaN(窒化ガリウム)パワー半導体について、基本的な設計技術や製造方法、ターゲット用途などの現状を説明する。 アクティブクランプ・フライバックで超高密度「USB PD 3.0」設計に対応

アクティブクランプ・フライバックで超高密度「USB PD 3.0」設計に対応

100Wのプログラマブル電源(PPS)向けUSB PD(Power Delivery) 3.0などの新しい用途や急成長するアプリケーションが、しばしば超高密度(UHD)であると言及される、より小型でコンパクトなスイッチング電源(SMPS)フォームファクタの需要を促進しています。 トップサイド冷却パッケージ採用MOSFET

トップサイド冷却パッケージ採用MOSFET

オンセミは、トップサイド冷却パッケージを採用したMOSFETデバイスシリーズを発表した。上面にサーマルパッドを設けており、PCBを介さずに直接ヒートシンクに放熱できる。 140dB超のダイナミックレンジを実現した8.3MピクセルCIS

140dB超のダイナミックレンジを実現した8.3MピクセルCIS

オンセミは、1/1.7インチで8.3MピクセルのCMOSイメージセンサー「AR0821CS」を発表した。eHDR技術を採用しており、140dB超のダイナミックレンジを達成。厳しい照明条件下でも高品質な画像を提供する。 4端子構成パッケージのSiC-MOSFET

4端子構成パッケージのSiC-MOSFET

三菱電機は、「SiC-MOSFET 1200V-Nシリーズ TO-247-4パッケージ」6品種のサンプル提供を2020年11月に開始する。4端子パッケージ採用により、従来品と比較してスイッチング損失を約30%低減した。

Copyright © ITmedia, Inc. All Rights Reserved.