電流出力型DACの消費電力を抑える設計手法:電源電圧の動的制御がカギ(3/4 ページ)

実測評価の結果

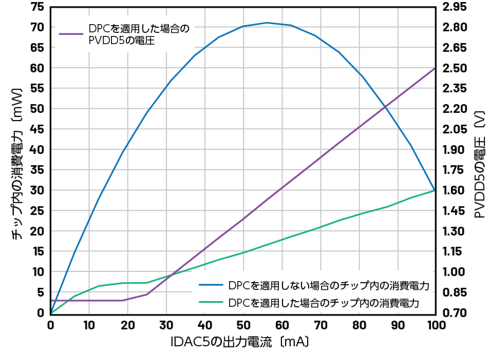

ここでは、図4の回路の評価結果を示します。図5は、IDACの1つのチャンネル(IDAC5)に注目して各値をプロットしたものです。このチャンネルは、22Ωの負荷を駆動できるように設計されています。フルスケールの電流範囲は100mAです。また、このIDACの電源電圧については、PVDD - AVEEが2.5V以上という要件を満たさなければなりません。最小ヘッドルーム電圧は0.275Vです。これらの条件を満たせるよう、マイコン上で稼働するファームウェアによって制御を行う必要があります。

チップ内の消費電力は、PVDDと負荷電圧の差を測定することで計算します。図5では、DPCを適用した場合と適用しない場合の値を示しました。DPCを適用しない場合のPVDDは2.5Vの固定値です。AVEEの値は0Vです。

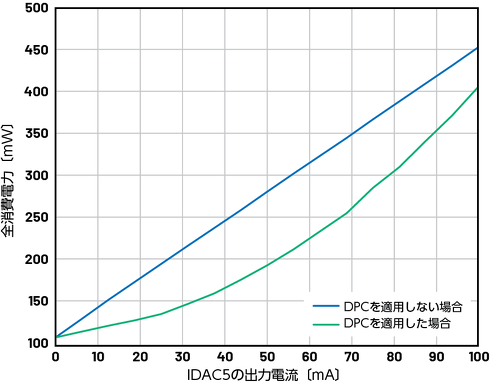

では、システム全体の消費電力はどのようになるのでしょうか。これについては、DC-DCコンバーターとIDAC(AVDDピン)に供給される3.3Vの電源の電流値を測定することで把握できます。図6は、0mAから100mAまでの全出力電流範囲における3.3V電源の全消費電力をプロットしたものです。

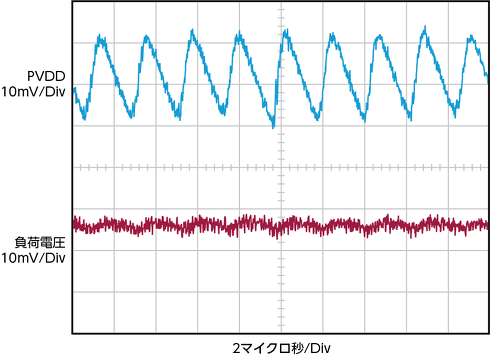

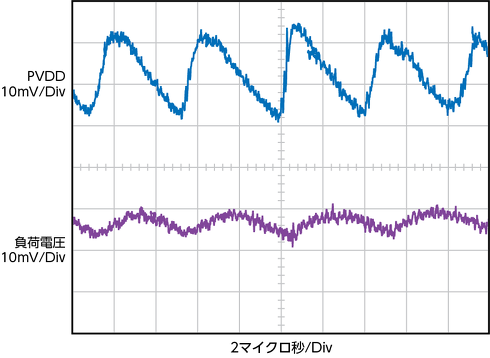

図7、図8に示したのは、PVDDピンとIDACのチャンネルの出力ピンで観測された電圧リップルです。図4に示したように、IDACはSIMOコンバーターの出力によって直接駆動されます。そのため、IDACのAC電源電圧変動除去比(AC PSRR)によっては、出力にある程度のリップルが現れることが想定されます。ここで、AC PSRRは、IDACに印加される電源電圧のAC的な変動が出力電流においてどの程度除去されるのかを表します。この種のリップルは、SIMOコンバーターの出力コンデンサーを最適化することでさらに低減できます。必要であれば、PMICの出力にフィルターを適用します。

図7、図8に示した結果は、SIMOコンバーターの出力とIDACの電源ピンの間にLCフィルターを適用した状態で取得したものです。なお、IDACは多くの電流をソース/シンクする可能性があります。従って、LCフィルター向けには等価直列抵抗(ESR)の小さいインダクターを選択するとよいでしょう。

Copyright © ITmedia, Inc. All Rights Reserved.