表舞台に上らなかった「世界初」のプロセッサ、MP944:マイクロプロセッサ懐古録(11)(2/2 ページ)

Garrett AiResearchやMP944のその後

残念ながらHolt氏に情報公開の承認を出した後も、米海軍あるいはGrumman(現Northrop Grumman)はCADCの詳細やMP944に関する情報を一切公開していない。Garrett AiResearchはその後AlliedSignalのエンジン部門になり、その後TextronのLycoming Turbine Engine Divisionと合併してAlliedSignal Aerospace Companyの一部となっており、こちらから情報が出てくる可能性もほぼ無い。そんな訳でHolt氏の信ぴょう性はともかくとして、複数ソースあるいは公式ソースが無いという事もあって、現時点でもIntel 4004が世界最初のマイクロプロセッサという評価になっているのはやむを得ないことかもしれない。ちなみにHolt氏によればMP944およびCADCは

- 世界初のマイクロプロセッサチップセット

- 世界初の航空宇宙用マイクロプロセッサ

- 世界初のFly by Wire飛行コンピュータ

- 世界初の軍事用マイクロプロセッサ

- 世界初の量産型マイクロプロセッサ

- 世界初の完全統合型チップセットマイクロプロセッサ

- 世界初の20bitマイクロプロセッサ

であることは間違いないと主張し、さらにHolt氏の主観では

- 世界初のBIST(Build-In Self Test)機能付きマイクロプロセッサ

- 世界初のDSPアプリケーションを実行できるマイクロプロセッサ

- 世界初のパイプライン動作をするマイクロプロセッサ

- 世界初の並列処理(コプロセッサを同時に利用できる)をサポートするマイクロプロセッサ

- 世界初のカウンタ内蔵ROM

であるとしている。この最後の項目だけはちょっと説明が必要だろう。ROMにはプログラムコードだけでなく、固定値のデータを含む場合があるが、そのデータアクセスのためにはアドレス指定が必要である。通常はCPU側でアドレス指定をして、そのデータにアクセスする訳だが、MP944のROMには内部にプログラムカウンタが設けられ、このプログラムカウンタの値を使ってROMへのアクセスが可能となっていた。カウンタにはインクリメントおよびプリセットの機能があり、これを使う事で回路の小型化に貢献したとしている。要するにROMにSRAMを組み合わせたハイブリッド型のROMだった訳だ。これは確かにちょっと珍しい。

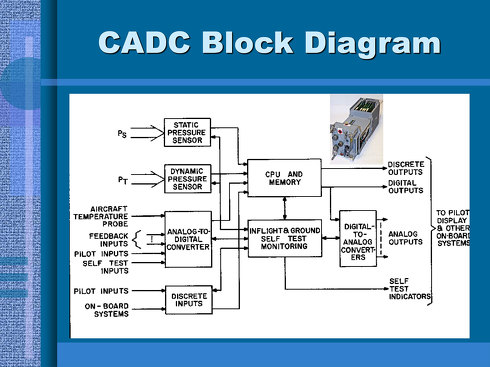

CADCの内部構造はこんな具合(図3)だ。

基本的な機能は高度・対気速度・昇降率・マッハ数・温度を計算して計器に表示するとともに、主翼(F-14は可変後退翼だった)のスイープ角と変形速度の計算と制御、主翼前縁スラットと後縁の機動フラップ、さらに初期型の機体で利用されていたグローブベーンの制御などを行った。また着陸あるいは攻撃時の迎え角の計算も担当している。こうして並べると簡単に見えるかもしれないが、例えば静圧測定では高度8万フィートにおいて1フィートの分解能が要求されており、これを実現するためには12bitの解像度を持つADCが必要だった。またセンサーの測定値は非線形(例えば圧力対高度特性とか圧力対周波数特性とか)だったので、センサーの測定値から望む数値を計算するためには6次の多項式を計算する必要があったとする。先に世界初のDSPアプリケーションとあったが、CADCはこの多項式を常に計算しながら結果を表示するとともに、その結果に応じて機体の制御を行う訳で、確かに現在ならばDSPアプリケーションと分類される処理である。ちなみに毎秒18.3cycleで処理できたというので、1回の処理はおおよそ54.6ミリ秒で済んだ計算になる(要求は毎秒16cycleだったらしいから、要求を上回る性能だった訳だ)

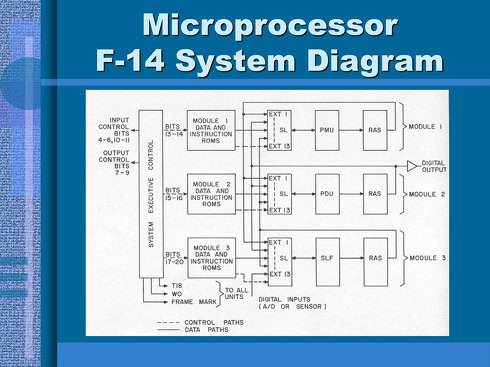

その図3で"CPU AND MEMORY"とある中身が図4だ。強いて言えばVLIW的な構造とでもいうべきだろうか? System Executive Controlは全体のタイミング制御を行うユニットで、ここからの信号を受けて3つのROMから命令およびデータをSLが読み込んで、それぞれPMU/PDU/SLFという実行ユニットに送り込み、その結果がRASに格納され、必要に応じて外部に出力が行われるという構造である。つまりこの6種類(ROMとRAMを除くと4種類)で、MP944というプロセッサが構成されたことになる。動作周波数は375KHz、つまり毎秒9370命令を処理可能になっている。データ幅は20bitの固定小数点で、パイプライン化したことで加減乗除はいずれも1cycleで実施できた。また平方根は毎秒73回、論理和/論理積も26回処理できたらしい。分岐も1cycleで処理可能だった。Pipelineといっても、データの依存関係は考慮する必要が無い仕組みだったから、ほぼDSP同様にZero overhead loopが実質的に可能だったようだ。

RASはRandom Access StorageでRAMの事。SLはSLU(Steering Logic Unit)の略で、これがCPUというかDecoder部的な処理で、その後にPMU(Parallel Multiplier Unit)/PDU(Parallel divider unit)/SLF(Special Logic Function)の各ユニットが並ぶ

RASはRandom Access StorageでRAMの事。SLはSLU(Steering Logic Unit)の略で、これがCPUというかDecoder部的な処理で、その後にPMU(Parallel Multiplier Unit)/PDU(Parallel divider unit)/SLF(Special Logic Function)の各ユニットが並ぶMP944の設計はそんな訳でGarrett AiResearchが担当したが、製造はAMI(American Microsystems Inc.)が担当。PMOSベースでの製造だったそうだが、プロセスなどはもはや不明だ(恐らくIntel 4004同様に10μmとかそのくらいの、かなり大きなものだったと想像される)。MP944は最終的に

- SLU(2313Tr):3個

- PMU(1063Tr):1個

- PDU(1241Tr):1個

- SLF(743Tr):1個

- ROM(3268Tr):19個

- RAS(2330Tr):3個

の合計28個、総トランジスタ数74442個だったとされる。ROMとRAMを抜いてもトランジスタ数は9986個になり、4004の2300個に比べるとはるかに巨大である。確かに当時の技術ではこれをワンチップ化することは不可能だっただろう。ただその分、性能も圧倒的である。3つの実行ユニットを同時に動かせたから、演算性能は28.1KFlopsに達している。この辺は4bitのIntel 4004とは比較にならない(4004はPipeline化されておらず、750KHz動作といっても実際には1命令の処理に8cycle掛かったから、もしMP944と同じ処理を行わせた場合の性能は多分2桁以上違っていただろう)

もっとも、MP944は本当に固定小数点演算と、簡単な出力制御しかできない(図3で分かるように、結果をデジタルないしDAC経由でアナログ信号で継続的に出力するだけで、その先はCADCにつながる別の機器が面倒を見た)し、プログラミング言語もデバッガも何もない(Holt氏はバイナリプログラミングを行った)。Microprocessorではあるが、汎用性にはかなり欠けるものではあった。軍用品ということもあり、動作温度範囲として−55℃〜+125℃が要求されたとか、CADC全体のコストを3000〜5000米ドル(1968年当時の価格:現在だと2万5000〜4万2000米ドルに相当)に抑えないといけなかったとか、消費電力はCADC全体で10W以下に抑える必要があったなど、かなりとがった特徴を持つCADCを構築するために、Holt氏が言うところの“世界最初のMicroprocessor”が使われた、という事実は記憶に留めておいても良いかもしれない。

⇒「マイクロプロセッサ懐古録」連載バックナンバー一覧

関連記事

登場して半世紀、多くの互換品を生んだIntel「80186/80188」

登場して半世紀、多くの互換品を生んだIntel「80186/80188」

1980年代初頭に登場したIntelのマイクロプロセッサ「80186/80168」は、多くの互換CPU/CPU IPを生んだ。発売後、半世紀近くがたった今でも、多くの組み込み機器で動作している驚異的なロングランのプロセッサである。 32年ぶりの新製品も 波乱万丈だったMotorola「MC6800」

32年ぶりの新製品も 波乱万丈だったMotorola「MC6800」

今回はMotorolaのプロセッサ「MC6800」を紹介しよう。開発から市場投入に至るまで波乱万丈な経緯を持つMC6800は、派生品も多く、一時代を築いた息の長いプロセッサである。 ファミコンにも採用された「MOS 6502」、その末路をたどる

ファミコンにも採用された「MOS 6502」、その末路をたどる

今回は、メーカーそのものが無くなり「一発屋」となってしまった「MOS 6502」を紹介したい。任天堂の「ファミコン」にも採用された製品だが、その末路は「会社がなくなったことによる断絶」だった。 一発屋で終わったけど抜群の影響力、TI「TMS1000」

一発屋で終わったけど抜群の影響力、TI「TMS1000」

今回はTexas Instruments(TI)が開発した「TMS1000」を紹介する。「MCUの最初の製品」とも称されるものだ。TIの製品としては短命だったが、IntelやMicrochip Technologyなどの製品に幅広く影響を与えた。 MCUの「礎」的存在、Microchip「PIC16」

MCUの「礎」的存在、Microchip「PIC16」

今回は、MCUを語る上で欠かせない存在であり、出荷数は累計数百億個に上るであろう「PIC」シリーズを語る。とりわけ「PIC16」は、アーキテクチャどころか製品としてもまだまだ現役である。 Intel「EMIB-T」で先進パッケージング促進へ

Intel「EMIB-T」で先進パッケージング促進へ

Intelが2025年4月に開催したイベント「Intel Foundry Direct Connect 2025」で注目度が高かったのが「EMIB-T」だ。チップ間をより効率的に接続できるようになるとする。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「通信エラー」の原因を追う――搬送機器のコントローラーを修理【前編】

- ARM台頭にルネサス誕生……時代に翻弄され続けた日立「SuperH」

- SDVとは? 定義や課題、時代に合わせたモビリティDX戦略の重要性

- フェライト(3) ―― 電子部品としてのフェライト

- Ankerがイヤホン用AIチップ、NORフラッシュベースCiM処理

- アルミ電解コンデンサー(1)―― 原理と構造

- 「解読不可能」を破る量子コンピュータ――今から始める暗号セキュリティ

- 低速センサーレス制御技術搭載、三相BLDCモーター駆動IC

- 次世代車載向けセキュリティコントローラー

- 15G〜20GHz対応のウィルキンソン電力分配/合成器、Vishay