部品の数を減らすコツ:Wired, Weird(2/2 ページ)

ORゲートの活用例

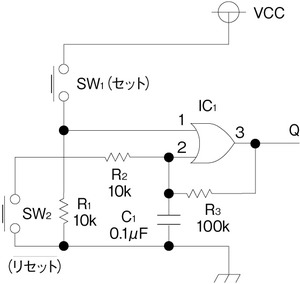

続いては、ORゲートの活用例として、図3のラッチ回路を紹介する。この回路では、電源を投入すると、IC1(「4071」を使用)の2番端子への入力は、コンデンサC1によってローに引かれ、IC1の出力がローになる。スイッチSW1(セット)をオンにすると、IC1の1番端子にハイが入力され、出力(3番端子)もハイになる。その出力信号は抵抗R3とC1を介して2番端子に接続されているので、C1×R3で決まる時間がたつと2番端子にハイが入力される。そのため、SW1をオフにしても2番端子への入力はハイに維持され、信号がラッチされた状態になる。スイッチSW2(リセット)を押すと、1番端子、2番端子ともにローが入力され、出力もローになってラッチが解除される。ラッチの感度(タイマー)はR3とC1の値で設定できる。図3の条件の場合、約10msのタイマーが構成されていることになる。

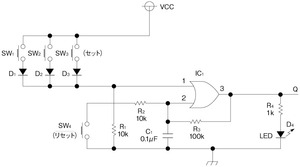

図4は、図3の回路を拡張してマルチ入力(3入力)のラッチ回路を構成したものである。この回路のように、スイッチとダイオードを増やすだけで、マルチ入力のラッチ回路を実現できる。

ここまでに示したように、抵抗、コンデンサ、ダイオードの使い方次第で、「ICと部品をうまく組み合わせて、さまざまな機能を実現する」ことができる。この考え方は設計変更を行う際にも便利なものだ。製品ができあがってから、何らかの追加や変更が必要になった場合に、この手法を使えば、比較的容易に変更が実現できるのである。

「ICと部品をうまく組み合わせて、さまざまな機能を実現する」ことにより、部品の数を少なく抑えることが可能になる。このようにディスクリート部品を使いこなすことは、頭の体操にもなり、ハードウエア設計の醍醐味を感じることもできる。

《次の記事を読む》

関連記事

連動しないインターフォンをつなぐ回路を考えた

連動しないインターフォンをつなぐ回路を考えた

自宅に2台のインターフォンがあるのだが、1台は玄関の呼び出しスイッチを押しても鳴らない。不便なので、2台とも呼び出しスイッチの音が鳴るように、連動させる回路を試行錯誤を繰り返し、作ってみたので紹介する。 DC/DCコンバータの周辺部品削減と安定化

DC/DCコンバータの周辺部品削減と安定化

PWM方式絶縁型DC/DCコンバータの高性能フィードバック回路は多くの場合、誤差増幅器が使用される。今回は、部品点数を削減し、安定性を高めることができるフィードバック回路を紹介する。 BroadR-Reach対応のコモンモードチョークコイル

BroadR-Reach対応のコモンモードチョークコイル

村田製作所は2016年9月、車載イーサネット規格「BroadR-Reach」に対応したコモンモードチョークコイル「DLW43MH」シリーズを発表した。独自の巻線技術でワイヤ間の静電浮遊容量バランスをコントロールすることにより、モード変換特性などを得ることに成功したという。 車載向け電源回路用インダクター、新たに3種追加

車載向け電源回路用インダクター、新たに3種追加

TDKは2016年9月27日、車載向け電源回路用のパワーインダクター「CLF-NI-Dシリーズ」で、新たに3種類のラインアップを拡大すると発表した。2016年10月から量産を開始するという。

Copyright © ITmedia, Inc. All Rights Reserved.