2Tbps帯域幅のFPGAをザイリンクスが出荷、バックプレーン伝送波形も公開:高速シリアルインタフェース技術

高性能有線通信アプリケーション向けの新型FPGA「Virtex-7 X690T」の伝送波形を公開した。28nm世代の半導体技術で製造するハイエンドFPGAファミリ「Virtex-7」のうち、13.1Gビット/秒のSERDESを80チャネル搭載した品種である。3月下旬にサンプル出荷を始めたばかりだ。

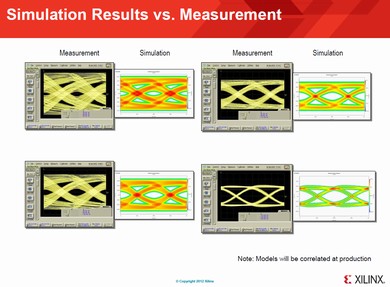

FPGA大手の米Xilinx(ザイリンクス)は2012年4月、高性能の有線通信アプリケーション向けに開発した新型FPGA「Virtex-7 X690T」の伝送波形を公開した。さらに、このFPGAを利用する通信システムの開発者向けに提供する開発ツール環境で同じ伝送波形をシミュレーションした結果も併せて公開し、実測結果との相関が高いことをアピールした。

Virtex-7 X690Tは、28nm世代の半導体プロセスで製造する最新のハイエンドFPGAファミリ「Virtex-7」のうち、最大13.1Gビット/秒で動作する高速シリアルトランシーバ(SERDES:シリアライザ/デシリアライザ)を80チャネル搭載した品種である。このデバイス単体で入出力帯域幅は2Tビット/秒に達する計算だ(13.1Gビット/秒×80チャネル×入力出力の2方向=2096Gビット/秒)。チップ間インタフェースや、「10Gbase-KR」をはじめとするバックプレーン通信、光変調モジュールを介した長距離ケーブル通信など、10Gビット/秒クラスの高速シリアル信号を伝送する用途に向ける。同社は、このデバイスのサンプル出荷を開始したと2012年3月28日に発表しており、2012年末までに量産出荷を始める予定である。

実測とシミュレーションの波形を比較 幾つかの異なる条件で実測波形とシミュレーション波形を比較した。両者の相関が高いことから、実際にこのFPGAを使うユーザーは実機の試作品を用意する前のシミュレーションの段階で、高い精度で波形を予測して設計を最適化できるという。出典:Xilinx (クリックで画像を拡大)

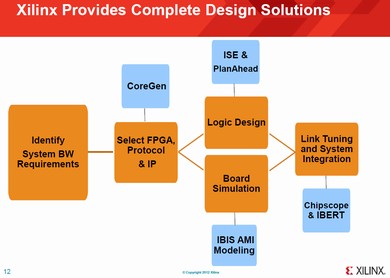

実測とシミュレーションの波形を比較 幾つかの異なる条件で実測波形とシミュレーション波形を比較した。両者の相関が高いことから、実際にこのFPGAを使うユーザーは実機の試作品を用意する前のシミュレーションの段階で、高い精度で波形を予測して設計を最適化できるという。出典:Xilinx (クリックで画像を拡大)Xilinxでプラットフォーム マーケティング 担当ディレクタを務めるブレント・プリツバス(Brent Przybus)氏は、「Virtex-7では、FPGAデバイス自体に加えて、高速シリアルインタフェースを組み込むボード全体の開発に必要な全ての要素をとりまとめて提供する」と述べる。

具体的にはまず、業界標準の各種プロトコルに対応した処理回路をユーザーが手早く開発できるように、さまざまなプロトコルに準拠した検証済みのIPコアを生成できるツール「CORE Generator」を提供する。さらに、高速信号を扱うプリント基板などの伝送線路シミュレーションに向けて、IBIS(I/O Buffer Information Specification)モデルのAMS(Analog Mixed Signal)バージョンやデバイスパッケージのSパラメータを提供する。これらのモデルをサードパーティ製の伝送線路シミュレータ上で組み合わせれば、実機の試作品を用意する前の段階で、データ伝送波形を高い精度で予測して設計を最適化できるという。

高速シリアルを組み込むボードの開発に必要な要素をまとめて提供 各種プロトコル規格に準拠した検証済みIPコアや、伝送波形のシミュレーションに用いるモデルなども提供する。出典:Xilinx (クリックで画像を拡大)

高速シリアルを組み込むボードの開発に必要な要素をまとめて提供 各種プロトコル規格に準拠した検証済みIPコアや、伝送波形のシミュレーションに用いるモデルなども提供する。出典:Xilinx (クリックで画像を拡大)加えて同社は、Virtex-7 X690Tとフットプリントの互換性を確保しつつ、13.1Gビット/秒SERDESの搭載数を96個に増やした上位品種「Virtex-7 X1140T」も準備しており、2012年5月にサンプル出荷を始める予定である。同デバイスの量産時期については、「当社では通常、エンジニアリングサンプルから量産まで11〜12カ月を要するので、それに従えば2013年第1四半期ころになるだろう」(同氏)と述べている。

関連記事

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング