第50回 「Qsys」で実現するシステム・レベル設計:FPGA Insights

最新のFPGAやASICは、システム・レベルの機能をワンチップに集積できるようになり、回路設計者にさまざまな可能性を提供している。半面、設計者はこれまで以上に生産性の向上が求められるなど、新たな課題に直面している。こうした中で開発ツールの機能が大きな進化を遂げている。

10年間で集積度は13倍以上に

半導体の微細加工技術の進化は、ICチップの高集積化や高性能・高機能化、低消費電力化を可能とした。今や、FPGAはその先導役を果たしているチップの1つである。例えば、アルテラのFPGA「Stratixシリーズ」では、2010年に発表されたStratix V FPGAの集積度が100万ロジック・エレメント(LE)を超えている。これは2002年に発表された最初のStratixに比べて、集積度が13倍以上に増加していることになる。

システム・レベルの設計を可能とする一方で、設計者は「設計する回路の大規模化」や「設計資産の再利用」、「回路の動作検証」などに対処するためのさまざまな課題を抱えているのも事実だ。このような問題を解決するためには有能な人材の確保が必要となるが、最近の経営環境を考えると、この対応はかなり難しい。このため、設計者は設計手法の改善や最新設計ツールの有効活用などによる生産性の向上が強く求められている。

本稿では、その一例してアルテラが提供しているFPGAとそのシステム統合ツール「Qsys」を用い、各種IPコアを活用したシステム・レベルの設計を効率よく行うための手法などを紹介する。

設計の抽象度を上げる

設計生産性を向上させるためにはいくつかの方法がある。その1つが設計の抽象化レベルを上げていくことである。かつて、ゲート・レベルで設計していた時代の論理ゲート規模はせいぜい数百ゲートであり、当時は回路図入力でも対応することができた。ところが半導体チップの微細加工が進むにつれ、FPGAに実装されるゲート規模も大きくなった。このため、1995年ごろより設計の抽象化レベルはRTL(レジスタ転送レベル)へと移行していった。

さらに、2000年ごろより高性能なプロセッサ・コアや大容量のメモリ・ブロックなどをFPGAに実装することが可能となった。これに対して、設計の抽象化レベルをRTLからIPレベルに引き上げることで、設計の生産性をさらに向上させようとする動きが出てきた。アルテラは、FPGA開発ソフトウェア「Quartus II」で利用できるシステム開発ツール「SOPC Builder」のサポートを始めることで、そのニーズに応えた。

2011年5月には、SOPC Builderの後継ツールとして「Qsys」が発表された。Quartus IIで利用可能なシステム・レベルの統合ツールである。Qsysは、SOPC Builderと比べて大きく異なる点が3つある。まず1つがNoC(ネットワーク・オン・チップ)アーキテクチャをベースとした高性能インタコネクトを採用していることだ。2つめはIPコアの再利用をより容易とする階層化構造をサポートした。3つめは業界標準インタフェースへの幅広い対応である。

それでは、最新のFPGA設計で直面している3つの課題(「設計規模の増大」、「設計資産の再利用」、「回路の動作検証」)に対して、Qsysが提供するソリューションを紹介する。

カスタム・ロジックの設計に集中

1つめは、設計する回路規模の増大である。だが実際には、作業量が増加しても設計者数や設計時間を十分に確保できないケースが一般的ではないだろうか。長引く景気の低迷により経営環境は悪化し、人員や開発費の削減などが行われたからだ。また、開発期間の短縮という要求も、設計者にとっては大きなプレッシャーとなっている。

限られたリソースで期待値以上の成果を上げるには、設計手法や作業自体を見直すことも必要となる。例えば、過去の設計資産やサードパーティが開発した標準IPコアの再利用、あるいは開発ツールがサポートする自動設計機能の有効活用、などである。

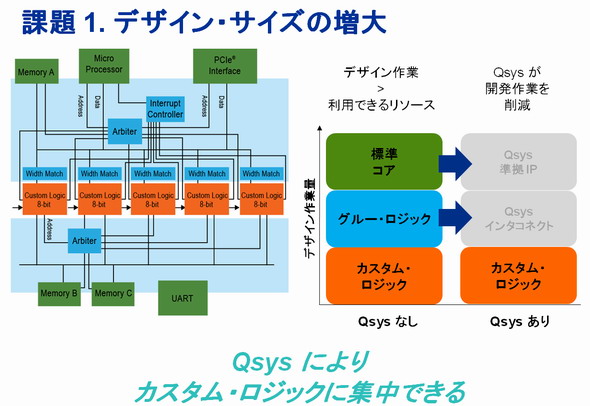

図1に示すように、システム・レベルの設計を行う場合、回路を大きく3つのブロックに分けることができる。その3つとは「標準コア」、「グルー・ロジック」、「カスタム・ロジック」である。Qsysを利用すれば、標準コアはIPとして再利用することが容易となる。IPコア間を接続するためのグルー・ロジックもツール側で自動生成することができる。その分、設計者はカスタム・ロジック部の開発に集中することができるというわけだ。この部分は製品競争力を高める(独自性を打ち出す)ブロックとなる。

アルテラはQsys準拠のIPコアを広範囲に提供している。既に利用できるQsys準拠のIPは100種類を超え、現在も増強中である。主なQsys準拠IPコアとしては、PCIeやTSE(トリプル・スピード・イーサネット)などの「インタフェース・プロトコルIP」、DDR/DDR2/DDR3といった「メモリIP」、スケーラやスイッチ、アルファ・ブレンディング・ミキサなどの「ビデオ/画像処理IP」、JTAG/UART/SPIなどの「組み込みIP」を用意している。

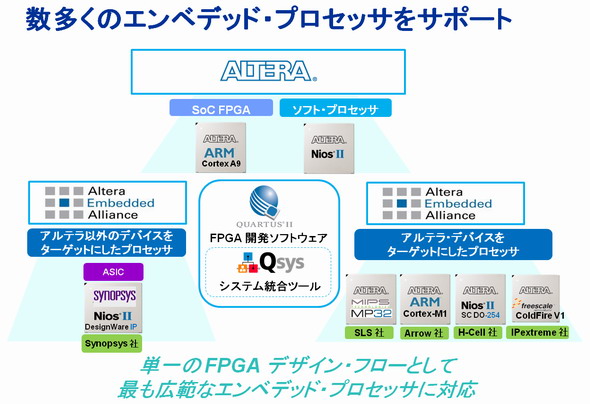

Qsysで対応する「組み込みプロセッサIP」も多様化するニーズに合わせて拡充している。独自アーキテクチャの「Nios II」をはじめ、「MIPS MP32」、「ARM Cortex-M1」、「freescale ColdFire V1」などがある(図2)。さらに、ハードウェアIPで「ARM Cortex A9」を実装したSoC FPGAも用意されるなど、単一のFPGAデザインフローで、用途に適したプロセッサIPを選択することが可能となった。

統合作業を自動化

標準IPコアを再利用することで、回路設計の生産性は格段に向上するが、回路が大規模・複雑化すれば、IPコア同士をつなぐバスラインの配線作業は繁雑となり、これを人手で行うと単純な配線ミスを起こす確率は高くなる。特に、異なるバス幅のIPコア同士を合わせ込んだり、割り込みの優先度を変更したりするときは要注意である。

Qsysでは、このような単調でエラーを起こしやすい統合作業の一部または全てを自動化することで、人的作業によるケアレスミスをなくせるようにした。しかもQsysでは、設計者が直感的に使えるGUIを用いてIPコア間の接続情報を入力すれば、Qsys側でHDL形式のインタコネクト情報が自動生成される。この機能はSOPC Builderも備えているが、Qsysでは階層設計にも適用できるよう機能が強化されている。

もう1つSOPC Builderとの大きな変更点を挙げるとすれば、Qsysはインタコネクトに「ネットワーク・オン・チップ(NoC)アーキテクチャ」を採用したことである(詳細はこちら)。Qsysインタコネクトは、パイプライン・レジスタの数を調整(ツール側で自動挿入)することで、SOPC Builderを使って設計した場合に比べて、FPGAの動作周波数を最大2倍に向上させることができる。

AXI3対応で設計資産の再利用を加速

2つ目の課題は、設計資産の再利用に関わることである。これまで社内に蓄積されてきた設計資産を流用したり、流通しているサードパーティ製IPコアを利用したりすれば、全ての回路を最初から設計する場合に比べて、開発の負荷を軽減したり、開発期間を短縮したりすることができる。ところが、IPコア同士を接続するためのインタフェースが独自規格であったり、仕様が古く変更されていたりすると、インタフェース部分の再設計が必要になることもある。特に、かつての日本では回路の設計情報が設計者個人の頭脳に記憶されているケースが多かった。このため、企業が文書やデータで管理していない場合は、設計者と異なる人が過去の設計資産を再利用しようと思っても、設計情報を理解するまでに多大な労力を必要とすることもあった。

Qsysでは、標準インタフェースを採用することで、このような課題を解決している。前述の通り、アルテラは「Avalonインタフェース」をサポートしてきた。

さらにQsysは、自社内に蓄積した設計資産をIP化して、FPGAでの再利用を加速するための「コンポーネント・エディタ・ツール」を搭載している。このツールを使って、ユーザー固有のRTL設計データをQsysのライブラリとして取り込むことができる。設計者はまず、QsysのGUIウィザードを利用して、設計データを自動的にパッケージ化する。その上で、再利用可能なIPコアとしてライブラリに追加することになる。このとき、IPコアをパラメタライズすることができるため、スケーラビリティも向上する。

こうした機能はSOPC Builderでもサポートされていた。Qsysでは、システムの階層化設計の機能が新たに追加された。この機能により、新たに登録されたIPコアを含めて複数のIPコアを統合した回路をサブシステムとして登録することができる。このサブシステムを別のシステムに再利用することで、設計の抽象度レベルをさらに高め、設計の生産性を向上することができる。

ブリッジIP内蔵で検証作業を容易に

3つ目の課題は、設計した回路の動作を検証するための作業負荷が増えてきたことである。ICチップの高集積・高機能化が進むにつれて、検証作業の重要性が高まり、その上作業時間も増大している。数百のレジスタを手動で設定して、大量のデータを解析するには膨大な時間が必要となる。回路設計に要するのと同等の時間を検証作業に費やすことも珍しいことではなくなった。設計の手戻りをできるだけ少なくして生産性を向上させるためにも、設計の上流工程における検証作業がより重要となってきた。

アルテラのFPGAには、JTAGやTCP/IPのブリッジIPが用意されている。このIPをFPGA内に組み込んでおけば、外部に接続されたパソコンを使って、FPGA内のレジスタやメモリへのアクセスが可能となる。つまり、Qsysのシステム・コンソールから、FPGAに内蔵したブリッジIPを介して機能ブロックのポートにアクセスし、外部からコマンドを送ったり、レジスタの状態を読み出ししたりすることができる。これらの機能によって検証作業が容易となり、ボード完成までの時間も短縮することが可能となる。

公開中(2011年2月〜2012年12月掲載分)

第27回 Altera社、28nmのFPGA製品群を拡充 さまざまなシステムの要求に対応

第30回 「システム設計者の選択肢を広げるSoC FPGA」(前編)

第31回 「システム設計者の選択肢を広げるSoC FPGA」(後編)

第41回 システムの要求に応える28nmFPGA(その1)〜高速シリアル伝送設計のためのトランシーバ・ツール・キット〜

第42回 システムの要求に応える28nmFPGA(その2)〜28nmFPGAデザインにおける消費電力の最適化〜

第43回 組み込みシステム設計者のニーズに応える最新SoC FPGA(前編)

第44回 組み込みシステム設計者のニーズに応える最新SoC FPGA(後編)

第45回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(前編)〜

第46回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(後編)〜

第47回 システムの要求に応える28nm FPGA(その3) 〜パーシャル・リコンフィギュレーションの設計〜

第48回 こんなところにCPLD――産業用途でみるCPLD活用事例(前編)

第49回 こんなところにCPLD――産業用途でみるCPLD活用事例(後編)

第51回 「Qsys」で実現するPCIeベースのFPGA設計

第52回 デジタル信号処理(DSP)設計の基礎知識を学ぶ 〜ビデオ信号処理編〜

第53回 デジタル信号処理(DSP)設計の基礎知識を学ぶ 〜産業機器向けモーター制御編〜

第54回 開発キットを今すぐ入手し、活用する!! 〜28nm「Cyclone V FPGA」、「Arria V FPGA」の価値を高める

第55回 開発キットを今すぐ入手し、活用する!! 〜28nm「Stratix V」FPGAの価値を高める

第56回 機能安全規格への適合とFPGA活用法 〜IEC61508とアルテラの取り組み〜

第57回 機能安全規格への適合とFPGA活用法 〜機能安全データ・パッケージ〜

関連情報

FPGAシステム設計における、ネットワーク・オン・チップ・アーキテクチャの利点

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年12月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。

図1 Qsysを活用することで、設計者はカスタム・ロジックの設計に集中することができる

図1 Qsysを活用することで、設計者はカスタム・ロジックの設計に集中することができる 図2 さまざまな組み込みプロセッサに対応

図2 さまざまな組み込みプロセッサに対応