第51回 「Qsys」で実現するPCIeベースのFPGA設計:FPGA Insights

PCIe(Peripheral Component Interconnect Express)インタフェースは、システムの性能や機能を向上させ、柔軟性/拡張性に優れていることから、さまざまな電子機器で採用されている。FPGAベンダーはPCIeインタフェースをハードIPで実装した製品群と使いやすい開発ツールを充実させることで、PCIeベースのFPGA設計を支援する。

ハードIPコアでPCIe搭載

PCIeは、大容量のデータを高速に伝送するためのI/Oシリアル・インタフェース規格で、ハイエンド・プロセッサ・システムの標準的なインタフェースの1つである。コンピュータ拡張規格として2002年にPCI-SIGが策定し、2003年にリリースされた。パラレル・バス方式のPCI規格が伝送速度の限界を迎える中で、PCIeは高速シリアル・インタフェース技術を採用することで、"高速データ伝送"という市場のニーズに応えていくこととなった。パラレル・バス方式に比べて、I/O数の削減にも寄与している。

こうした動きに対して、デバイスメーカーはPCIeソリューションの提供にどのように関わってきたのだろうか。アルテラの場合、5年以上も前からPCIeソリューションを開発してきた。例えば、トランシーバを搭載していないFPGA向けのソフトIP(PIPEインタフェース)と、トランシーバを内蔵したFPGA「Stratix GX」用ソフトIPの2種類を第1弾として用意した。

現在では、全ての40nm/28nm FPGAファミリでハードIPコアのPCIe搭載品を準備している。例えば、PCIe Gen1×1/×4/×8用のハードIPをサポートする低コスト40nm「Arria II GX FPGA」、PCIe Gen2のハードIPをサポートする「Stratix IV FPGA」、PCIe Gen3用のハードIPをサポートする「Stratix V GX FPGA」などがある(図1)。

これらの製品は、PCI-SIGインテグレーターズ・リストに記載されており、さまざまなマザーボードやチップセットとの相互運用性を検証済みである。さらに、設計者が使いやすいようにPCIe IPコアをより使いやすくするため、さまざまなPCIeベースの開発キットやAvalon-MMインタフェース、Qsysといったソフトウェア・ツールが準備されている。

前回の「『Qsys』で実現するシステム・レベル設計」でも述べたが、システム・レベルの設計効率を高めるには、設計資産を再利用することが有効な手段の1つである。例えば、アルテラが提供するPCIeハードIPを活用することで、設計者はさまざまなメリットを享受できる。まず、内蔵されたPCIeのIP自体が既に動作検証を終えている点だ。タイミング収束で苦労することもない。高性能なチップになればなるほど動作タイミングの問題は重要な要件となる。その動作が事前に保証されているため、検証作業を軽減することができる。

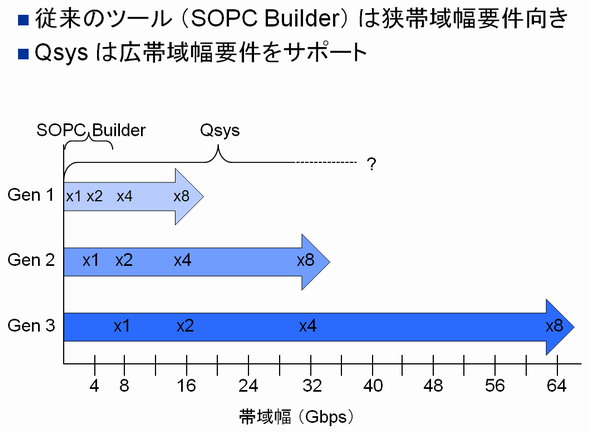

次に、アルテラではハードIPでありながら、柔軟なソリューションを提供している。データ幅は1レーンから最大8レーンまで、データ・レートはデバイス・ファミリにもよるがGen1/2/3に対応している。また、ハードIPはルート・ポートおよびエンド・ポイント構成のいずれでも実装することができる。さらに、QsysはSOPC Builderに比べて広帯域幅の要件にも対応できるようになった(図2)。オプション設定を行うために使いやすいパラメータ入力ツールも用意されている。IPはハードマクロ化されているため、Gen3×8レーンの場合で最大10万ロジックエレメント(LE)相当を削減できるなど、コストの低減にも貢献している。

PCIeとユーザー・ロジック部のインタフェースとしては「Avalon-ST」と「Avalon-MM」の2種類をサポートしており、いずれかを選択できる。Avalon-STインタフェースは、ユーザー・ロジックで作り込むこともできるため、用途に応じてPCIe帯域幅を最適化することができる。ただし、最適化するためには、PCIeプロトコルに関する十分な知識が設計者に必要となる。

一方、Avalon-MMインタフェースは、シンプルなアドレスとデータ・インタフェースが提供されるため、PCIeプロトコルに関する詳細な知識はいらない。リードやライトといったコマンドやアドレス、データなどから成るTLP(トランザクション・レイヤ・パケット)のエンコーディングおよびデコーディングを自動化したことによって、PCIeの専門知識の必要性を大幅に軽減できる。さらに、帯域幅は少し犠牲となるが、PCIeとのインタフェースをユーザー・ロジックで作り込む場合に比べて、1カ月以上のエンジニアリング工数を削減することが可能となる。

PCIeユーザーがシステム設計にQsysを利用するメリットはいくつかある。その1つはQsysがシステムの階層化設計をサポートしていることだ。この機能により、PCIeシステム自体をサブシステムとして登録しておけば、ほかのデザインに再利用することが容易となる。もう1つは、複数のクロック・ドメインが存在するPCIeにもQsysは柔軟に対応できることだ。一般的なPCIeシステムには、クロック要件が異なるコンポーネントやインタフェースが含まれることがある。そういうケースでも、Qsysが自動的にブリッジを挿入し、対応してくれる。動作周波数をさらに引き上げて、システム性能を向上させたい場合もこの機能は有効である。

Qsysに関連するワークショップなども随時開催されている。ワークショップではQsysによる設計演習も予定されており、PCIe設計に興味のある技術者は、最新の情報を入手するため受講してみたらどうだろうか。

公開中(2011年2月〜2012年12月掲載分)

第27回 Altera社、28nmのFPGA製品群を拡充 さまざまなシステムの要求に対応

第30回 「システム設計者の選択肢を広げるSoC FPGA」(前編)

第31回 「システム設計者の選択肢を広げるSoC FPGA」(後編)

第41回 システムの要求に応える28nmFPGA(その1)〜高速シリアル伝送設計のためのトランシーバ・ツール・キット〜

第42回 システムの要求に応える28nmFPGA(その2)〜28nmFPGAデザインにおける消費電力の最適化〜

第43回 組み込みシステム設計者のニーズに応える最新SoC FPGA(前編)

第44回 組み込みシステム設計者のニーズに応える最新SoC FPGA(後編)

第45回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(前編)〜

第46回 最先端の28nmFPGAと最新のエンベデッド・ソリューション 〜ET2011リポート(後編)〜

第47回 システムの要求に応える28nm FPGA(その3) 〜パーシャル・リコンフィギュレーションの設計〜

第48回 こんなところにCPLD――産業用途でみるCPLD活用事例(前編)

第49回 こんなところにCPLD――産業用途でみるCPLD活用事例(後編)

第51回 「Qsys」で実現するPCIeベースのFPGA設計

第52回 デジタル信号処理(DSP)設計の基礎知識を学ぶ 〜ビデオ信号処理編〜

第53回 デジタル信号処理(DSP)設計の基礎知識を学ぶ 〜産業機器向けモーター制御編〜

第54回 開発キットを今すぐ入手し、活用する!! 〜28nm「Cyclone V FPGA」、「Arria V FPGA」の価値を高める

第55回 開発キットを今すぐ入手し、活用する!! 〜28nm「Stratix V」FPGAの価値を高める

第56回 機能安全規格への適合とFPGA活用法 〜IEC61508とアルテラの取り組み〜

第57回 機能安全規格への適合とFPGA活用法 〜機能安全データ・パッケージ〜

関連情報

FPGAシステム設計における、ネットワーク・オン・チップ・アーキテクチャの利点

Copyright © ITmedia, Inc. All Rights Reserved.

提供:日本アルテラ株式会社

アイティメディア営業企画/制作:EDN Japan 編集部/掲載内容有効期限:2013年12月31日

FOR FPGA BEGINNERS [PR]

■FPGAとは

■無償ではじめるFPGA設計

FPGA LEARNING CENTER [PR]

FPGAについて、基礎からわかりやすく解説しています。

初級者から熟練者まで、FPGA設計技術を向上させたいすべての人のためのトレーニング講座。

オンライン講座は視聴無料です。

図1 アルテラFPGAがサポートしているPCIeハードIP

図1 アルテラFPGAがサポートしているPCIeハードIP 図2 PCIeの帯域幅とQsys

図2 PCIeの帯域幅とQsys