PCI Expressの概要と高速化を支える技術:高速シリアル・インターフェイス入門(4)(3/3 ページ)

テスト・フィクスチャ

PCI Expressでは、半導体の規格であるBase Specification、半導体をシステムとして組み込んだCEM(Card Electromechanical)specification があり、CEM Specificationに基づいて試験方法を記載したTest Specificationが制定されます。

PCI Express Work Shopというイベントが年4回(米国で2回、台湾で2回)行われ、Test Specificationに基づいた試験が行われます。この試験に合格した製品はIntegrator Listに登録されPCI-SIGのWeb-Siteに掲載されます。なお、アイパターンなどの信号評価にはPCI-SIGが作成するSIGTESTと呼ばれるプログラムを使うことが求められます。

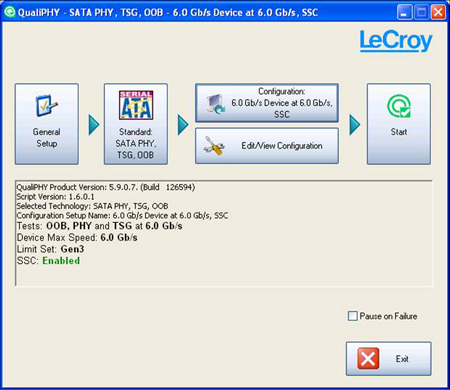

図8にはレクロイ社のコンプライアンス自動試験パッケージQualiPHY-PCIeのメインメニューを示していますが、PCI-SIGから配布されたDLLバージョンのSIGTESTが組み込まれています。

コンプライアンス・パターン

上記のコンプライアンス試験で使うコンプライアンス・パターンが規定されていますが、PCI Expressでは試験の実施を簡便化するために、コンプライアンス・パターンの発生に特別の機器を必要としません。送信レーンが抵抗で終端されていれば自動的にチップがコンプライアンス・モードに入りコンプライアンス・パターンを発生するように規定されています。

従って前述のCBBに試験をするアドインカードを挿してオシロスコープを接続するとオシロスコープが終端の役目を果たし、電源を入れればコンプライアンス・パターンの観測ができるようになっています。

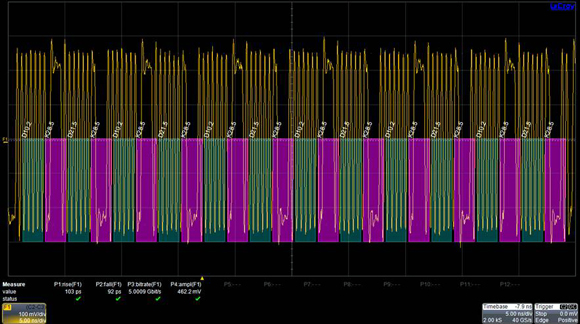

PCI Expressのコンプライアンス・パターンは8b/10bエンコードに従い、K28.5、D21.5、K28.5、D10.2の繰り返しであると規定されています。図9にコンプライアンス・パターンを示していますが、8b/10bデコード機能を用いると、正しいコードが送られているのが簡単に確認できます。Gen2に対応した機器の場合にはGen1にも対応しなければならないため、電源を入れるとGen1の2.5Gbpsで動作します。CBBのボタンを押すたびにGen2の5Gbpsでデエンファシスが3.5dB、5Gbpsでデエンファシスが6dBの3種類が( Gen1対応と合わせて3種類)切り替わるようになっています。

ここでは、PCI Expressの概要とその計測例をいくつか示しました。次回(最後回)はUSB 3.0を取り上げますが、PCI Express Gen2をベースにして作られた規格なので、ここで示した技術課題と同じものがありますが、USB 3.0特有の評価技術がありますので、今回の復習も加えながら紹介していきたいと思います。

関連記事

インターフェースIC活用のススメ

インターフェースIC活用のススメ

ロジックICの電源電圧の低下に伴い、インターフェースICの重要性が増してきた。現在では、単なる負荷駆動の手段ではなく、より効率が良く、より安全な信号伝送の手段としてその価値は高まってきている。本稿では、まずインターフェース回路の基本を再確認した上で、各種インターフェースICの果たす役割や最新の製品動向を紹介する。 PCI Expressの可能性を探る

PCI Expressの可能性を探る

PCI Expressは拡張性に富み、かつ低コストであることから、基幹系ネットワーク機器の設計において魅力的な選択肢となる。次世代の基幹系ネットワークでは、高コストな独自構造のバスに代わってPCI Expressが選択されるようになるかもしれない。

Copyright © ITmedia, Inc. All Rights Reserved.

図8 SATAのコンプライアンス試験プログラムの例

図8 SATAのコンプライアンス試験プログラムの例 図9 PCI Expressのコンプライアンス・パターン

図9 PCI Expressのコンプライアンス・パターン