入力インピーダンスの高いアンプの静電気保護:Design Ideas アナログ機能回路(2/2 ページ)

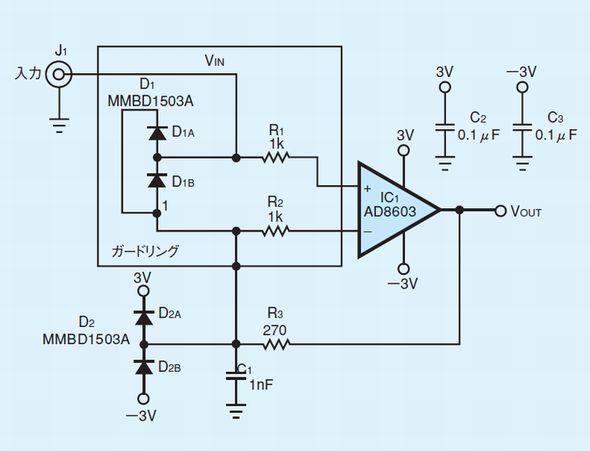

ESDが発生すると、大きなスパイク電圧が生じる。そのスパイク電圧の極性により、D1AあるいはD1Bが導通し、正または負の電源に向かって放電が起きる。このとき、コンデンサC1、ダイオードD2A、D2Bの接続点に大きな電圧が加わることになるが、D2AあるいはD2Bが導通するまでの間は、C1が放電電流の電荷を一時的に蓄積する。最終的にD2AあるいはD2Bが導通状態になると、放電電流が正または負の電源に向けて流れ、電荷が吸収される。また、コンデンサC1による電荷の蓄積効果により、スパイク電圧の立ち上がりが緩和され、IC1の出力部のラッチアップが回避される。コンデンサC1は、実際にはダイオードD1A/D1Bの浮遊容量が加わった値となる。この容量性負荷に起因してオペアンプIC1が発振する可能性があるが、それはR3の効果によって回避される。

ESDの発生時には、入力部(VIN)の電圧が電源電圧範囲を超えることがある。しかし、この回路であればD1A/D2AかD1B/D2Bが導通するため、その程度は2個のダイオードの順方向電圧ドロップ分だけで済む。従って、抵抗R1とR2を使用すれば、オペアンプへの入力電流をメーカー推奨の最大値である5mA以下に制限できる。

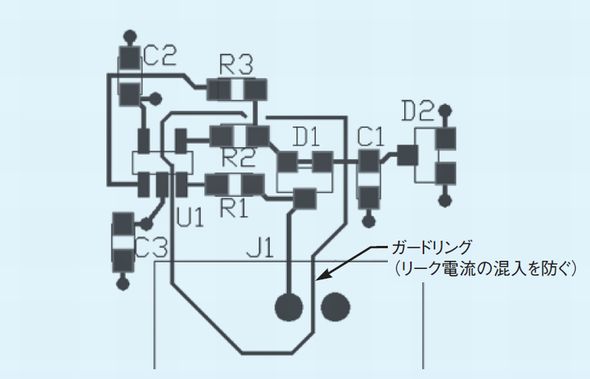

回路実装におけるプリント基板の注意点

図2の回路の実装においては、ESD対策として、特にプリント基板に関していくつか注意を払う必要がある。1つはプリント基板自体の問題である。プリント基板の絶縁抵抗が不均質だと、その部分が不要なリーク電流のパスとなるので注意しなければならない。もう1つの注意点はプリント基板のパターンである。基板の両面に、高インピーダンスの部分を取り囲むようにガードリングパターンを形成し、リーク電流が信号ラインに混入しないようにしなければならない(図3)。

Design Ideas〜回路設計アイデア集

【アナログ機能回路】:フィルタ回路や発振回路、センサー回路など

【パワー関連と電源】:ノイズの低減手法、保護回路など

【ディスプレイとドライバ】:LEDの制御、活用法など

【計測とテスト】:簡易テスターの設計例、旧式の計測装置の有効な活用法など

【信号源とパルス処理】:その他のユニークな回路

※本記事は、2008年7月29日にEDN Japan臨時増刊として発刊した「珠玉の電気回路200選」に掲載されたものです。著者の所属や社名、部品の品番などは掲載当時の情報ですので、あらかじめご了承ください。

「珠玉の電気回路200選」:EDN Japanの回路アイデア寄稿コラム「Design Ideas」を1冊にまとめたもの。2001〜2008年に掲載された記事の中から200本を厳選し、5つのカテゴリに分けて収録した。

関連記事

消費電流がマイクロアンペア台と少ないタイマー回路

消費電流がマイクロアンペア台と少ないタイマー回路

今回はマイクロプロセッサ、液晶ディスプレイ、32.768kHz水晶振動子を各1個とわずかな部品で簡単に構成したカウントダウン・タイマーを紹介する。電池を注意深く選択し、マイクロプロセッサの低電力モードを入念に開発することで消費電力を最小にし、電池寿命を最大にすることができる。 D-Aコンバータの出力を差動出力に変換する

D-Aコンバータの出力を差動出力に変換する

ハイエンドのD-Aコンバータを使う必要がないアプリケーションにおいて、シングルエンド出力のD-Aコンバータと外部回路を組み合わせて、必要十分な差動出力回路を構成できる回路を紹介する。 容量センサーの低域遮断周波数問題を解く

容量センサーの低域遮断周波数問題を解く

容量センサーのアナログ周辺回路を設計するときに最初に直面する問題は、低域遮断周波数だ。理論的には、初段のプリアンプの入力インピーダンスを大きくするといい。しかし、簡単に見えるこの設計要求の陰には、数多くの問題が待ち構えている。 高速な電圧-電流変換器として動作する回路

高速な電圧-電流変換器として動作する回路

電圧-電流変換器や高精度で帯域幅の広い可変利得のカレント・ミラーとして動作する回路を紹介する。高速ICや電流出力型D-Aコンバータの入力を備えたデバイスのテストなどに向けた回路だ。

Copyright © ITmedia, Inc. All Rights Reserved.