RMS位相ジッタ・バジェットにおけるマージンを拡大する方法:複数の周波数/出力に対応するデバイスで簡単に(3/3 ページ)

別のシステムにリファレンス・クロックを供給

プログラマブル・クロック回路は、動作中に周波数マージニングを実行する機能を備えています。出力周波数が異なることによりクロストークが生じますが、その影響も含めて0.7p秒のRMS位相ジッタ性能を達成しています。

RMS位相ジッタが0.7psに抑えられているということは大きな設計マージンを確保できるということを意味します。通信システムを例にとると、ジッタはビット誤り率(BER)に影響を及ぼします。RMS位相ジッタが大きいほどBERが高くなり、システム全体の性能が低下します。RMS位相ジッタが小さければ、設計者はジッタ・バジェットにおいて大きなマージン/余裕度を確保することができます。

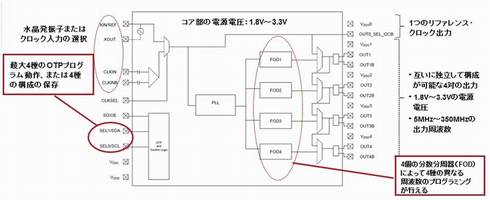

例に挙げたICでは、独立した4個の分数分周器を内蔵しています(図4)。

これらの分周器には、出力周波数の変更や、それによる周波数マージニングを行うために、シリアル・バスを介してアクセスすることができます。例えば、設計者が100MHzの出力周波数を扱っている場合、99MHz〜101MHzの範囲を小数点以下の単位で周波数を増減させることが可能です。

周波数マージニングをテストで活用

周波数マージニングはテストの段階でよく使用されます。多くの機器メーカーは、システムのテストの段階で周波数マージニングを行って堅牢性を確認します。例えば、機器メーカーがメモリを動作させるために、100MHzの周波数を仕様で定めていたとします。そうした場合に、テスト用のプログラムの中で、クロック・ジェネレータの出力周波数にある割合のマージンを持たせて、システムの堅牢性を評価したいといったケースがあります。例えば、10%の周波数マージンの範囲で周波数を1%ずつ増減させるといった具合です。

通常のアプリケーションでは、周波数の値は一定のまま保ちます。つまり、周波数マージニング機能は、ほとんどのアプリケーションにおいて試作品のテストの段階で使用されるものです。例に挙げたICなどでは、グリッチを発生させることなく周波数マージニングを実行することができます。設計者は文字通り、ある周波数範囲内で中心周波数から少しずつ周波数を変えることができますが、その出力にはグリッチが全く発生しません。このことは、システムの堅牢性を確認するために数多くのテストが実行される試作段階においては非常に重要なことです。

設計時に考慮すべきトレードオフ

組み込み設計者は、クロック・ジェネレータを選択する際、アプリケーションの観点から性能、消費電力、寸法の要件について検討します。重視するのは、プロセッサやFPGA、スイッチ、ブリッジなど、クロックの供給先となる設計上のエンドポイントについてです。どこに供給するクロックにもジッタに関する要件が存在します。また、設計者はジッタの要件だけでなく、消費電力の要件も慎重に確認します。

例えば、PCIベースのプラグイン・カードでは、25Wが上限といった具合に消費電力に制限があります。組み込み設計者は全体の要件を見極めた上で、何が最も重要なのかを理解しなければなりません。確かなことは、ジッタの要件は確実に満たさなければならないということです。さもなければ、BERが高くなり、システム性能が犠牲になってしまうからです。また、携帯型の機器のように消費電力の要件が厳しい場合には、クロック・ジェネレータについても消費電力が極めて重要な要素になります。

まとめ

旧来のクロック・ジェネレータを使用する場合、システム設計者/組み込み設計者は、異なる4種の高速クロックが必要であれば、最大4個の異なるクロック源または水晶発振器を1つの基板上に実装していました。それに対し、最新のクロック・ジェネレータでは、最も重要なポイントである集積化が進んだことから、4種のクロックを1つのチップで出力することができます。これにより、消費電力の低減、基板面積の削減、さらにはシステムのエンドポイントで要求される全ての性能目標の達成といった要求に対応可能になっています。

関連記事

位相ジッタ最大値400フェムト秒の高性能水晶発振器

位相ジッタ最大値400フェムト秒の高性能水晶発振器

IDTは、高性能・低位相ジッタの水晶発振器「XU/XLファミリー」を発表した。位相ジッタは、通常で300フェムト秒、最大値で400フェムト秒となる。 ジッタと位相ノイズの測定にPLLの分周器を活用

ジッタと位相ノイズの測定にPLLの分周器を活用

通信チャネルのデータ伝送速度が向上し、クロック信号の速度が高まるにつれて、ジッタと位相ノイズを高い精度で測定することがますます重要になっている。一方、測定の難易度は増すばかりで、高いコストが掛ってしまう。そこで本稿では、PLL ICの分周機能を活用して、測定器の性能限界を高める手法を紹介する。 誤解していませんか!? クロックジッターの「真実」を解説

誤解していませんか!? クロックジッターの「真実」を解説

第5回では、デジタルオーディオのクロックジッターに焦点を当て、その定義や測定法、オーディオ特性との関係について詳しく解説する。「クロックジッター」と一言で表現しても、クロックとジッターには多くの種類がある。オーディオ特性への影響を評価する際には、「どのクロック」の「どのようなジッター」かをきちんと説明できることが大切だ。 消費電力と専有面積を最大90%削減、PCIeタイミング製品に1.5V品追加

消費電力と専有面積を最大90%削減、PCIeタイミング製品に1.5V品追加

IDT(Integrated Device Technology)は、PCI Express(PCIe)タイミング製品群に、動作電圧が1.5VのクロックジェネレータIC「9FGU」とクロックマルチプレクサIC「9DMU」を追加した。デジタル一眼レフカメラや多機能プリンタ、車載インフォテインメント機器などの用途に向ける。 ジッター測定時のオシロのセットアップ

ジッター測定時のオシロのセットアップ

Copyright © ITmedia, Inc. All Rights Reserved.